Tool/software:

Hello ,TI team

i want to know the V5A&V5D noise and ripple requirement of TPS92520,the datasheet does not show this content,

or the TPS92520 V5A&V5D do not care the ripple and noise,right?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello ,TI team

i want to know the V5A&V5D noise and ripple requirement of TPS92520,the datasheet does not show this content,

or the TPS92520 V5A&V5D do not care the ripple and noise,right?

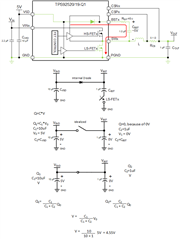

We do have recommended min V5D input capacitance that is a function of the bootstrap capacitor used, where we state a 10x rule which is designed to ensure when the bootstrap capacitor (Cbst) is charged up the V5D supply doesn't droop down low enough to trigger UVLO of V5D/A. For example if Cbst is 0.47 uF, then V5D input capacitance should be 4.7uF. We also recommend a 0.1 or 0.01uF capacitor in parallel at the pins for minimizing ripple and noise.

Where did you get 5% ripple from??? for the most part the ripple is small and it is a don't care if you follow the recommendations in the applications circuit.

OK,i need the ripple criterion of V5D&V5A,as we know,different supplier capacitors have different DC bias value ,if we change the supplier from A to B,we don't take the capacitor DC BIAS into account in TPS92520 circuit?

5% ripple is acceptable for peak to peak ripple but you must adhere to the 10x of Cbst (boost strap capacitor) guidelines for V5D/A capacitance. Cbst gets charged by V5D/A capacitance and we need to avoid having the voltage on V5D/A from hitting UVLO (4 V) with some margin during the charging of the boost strap capacitor (Cbst) by the LS FET. It is a simple charge balance equation. Below you see if you use 10x rule then V5D never gets below4.55V. Given the larger capacitance needed for this requirement the rippl should be very small, less than 5%.