Tool/software:

Hi,

We have been adjusting the peripheral components of the TPS12F1 but have not been able to achieve the expected performance. We would appreciate your support on the following inquiries:

-

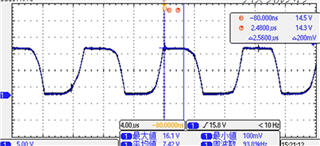

We understand that if the input noise level is too high, the AEF output may saturate. If the INJ pin voltage waveform appears as a square wave, does this indicate that the AEF output is in saturation?

-

If the INJ waveform is sinusoidal, can we assume that the AEF is not in saturation? Also, when considering a square wave as a saturated waveform, increasing the capacitance between Line-FG has changed the waveform from a square wave to a sinusoidal wave. However, the current capacitance value is significantly large, making it impractical for mass production. Are there any other methods to suppress saturation besides increasing the Line-FG capacitance?

-

Using PSPICE for TI, we simulated a frequency close to the PFC operating frequency (80kHz). The simulation results showed a square wave at the INJ pin, similar to actual operation. Furthermore, in the simulation, when the oscillation frequency is set below 100kHz, the INJ output waveform consistently appears as a square wave. Could you explain the reason behind this phenomenon?

-

The datasheet states that "to avoid amplification of low-frequency noise, the VDD ripple voltage should be kept within ±20mV." Currently, we are supplying power through an LDO from a DC power source, but due to switching noise, the ripple exceeds 20mV until it stabilizes. Is it mandatory to keep the ripple voltage within ±20mV?

-

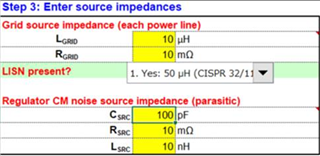

The "Regulator CM noise source impedance (Csrc, Rsrc, Lsrc)" in the Quick Start Tool appears to refer to the impedance of the AC/DC power supply stage after the filter. Could you provide guidelines on the typical values for these parameters?

We appreciate your time and support. Looking forward to your response.

Best regards,

Conor