Tool/software:

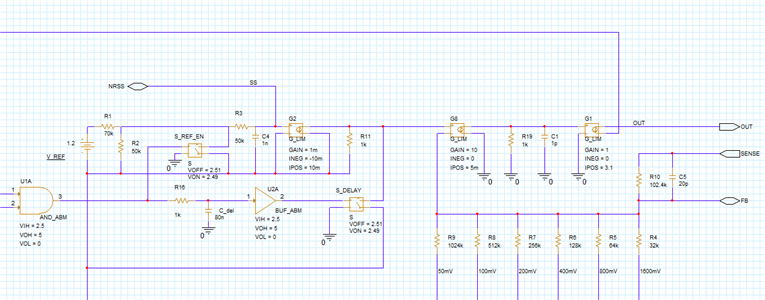

I noted that for the models available on the product page that the Soft Start feature does not appear to be implemented. This is stated in the encrypted model example for PSPice for TI, and demonstrated in LTSPICE for the unencrypted model by varying the SS capacitance from OPEN to 1uF, which is the stated full range in the data sheet. Inspection of the model file shows the following - and only line related to the SS pin:

R_TPS7A7200_R_NR_SS SS 0 1G

I am attempting to reduce the output current during startup to an acceptable limit based on the capacitance and other elements in my circuit. However, I cannot determine what the relationship is for Imax during the startup condition.

Was this intentional, and if so, can the model be updated to include the function? I need to show that my SS implementation has an acceptable margin against the IC max Iout, and is able to satisfy the requirements of other circuit elements of the voltage ramp rate.