Other Parts Discussed in Thread: BQSTUDIO, BQ76942

Tool/software:

Hi all,

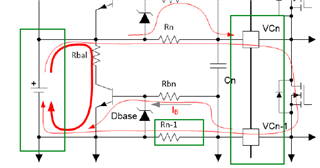

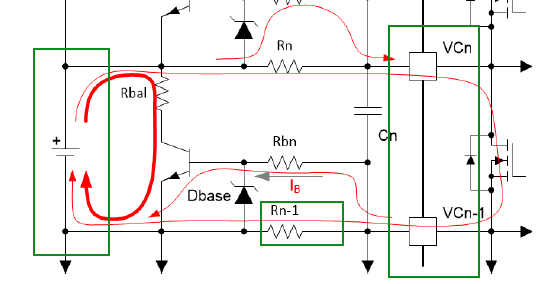

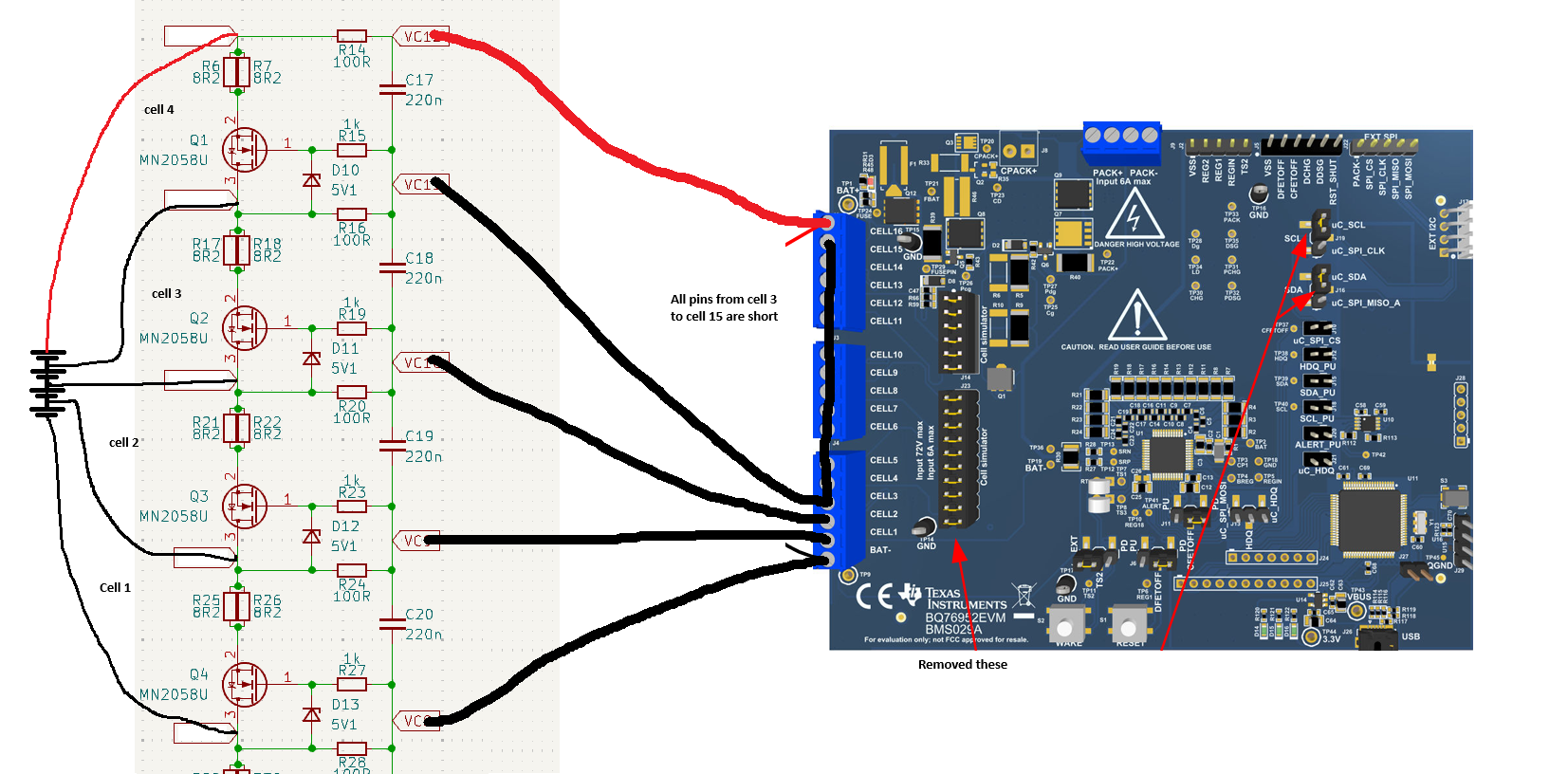

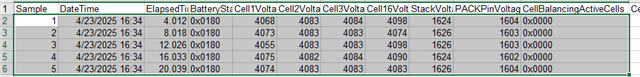

I'm working with the BQ76952EVM IC and trying to implement external cell balancing for a 4S battery pack. I’ve encountered an issue where balancing does not stop properly and all cells including the lowest voltage cell are being discharged continuously, which shouldn't happen.

Details:

-

Battery config: 4S

-

Balancing method: External FETs

-

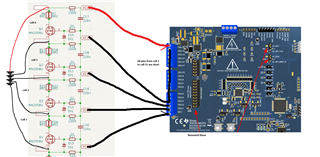

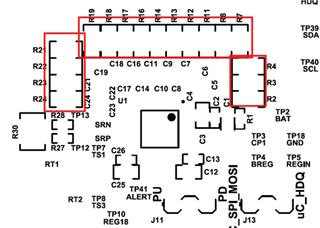

Test setup: Connected VC1 to VC4 properly, and VC5 to VC16 are shorted to VC4 since it's only a 4-cell configuration.

-

Observation:

-

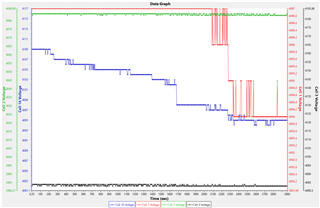

Balancing starts correctly, but does not stop, even for the lowest voltage cell.

-

Cell voltages keep reducing and fluctuating.

-

-

When using internal balancing, the behavior is as expected: balancing stops when the cells are within the desired threshold.

-

I'm using TI’s configuration tools and have tuned the thresholds as per datasheet recommendations.

-

I've attached the log file for reference.

What I need help with:

-

Is there any known issue or extra configuration required specifically for external balancing that is different from internal balancing?

-

Should additional settings be modified when shorting unused VCx pins for a 4S configuration?

-

Any suggestions for debugging why the lowest cell is being balanced?

Any insight or similar experience would be really helpful!

Thanks in advance,