Tool/software:

Hi,

We are currently evaluating a power supply circuit using LM5177DCPR, based on the schematic shown in Figure 8-1 of the Rev.F datasheet.

We would like to ask for your technical insight regarding the following two points observed during the test.

[Question 1]

During output short-circuit testing in buck-boost mode, we observed that the gate voltages of Q1 (input high-side) and Q3 (output high-side) fluctuate simultaneously.

As shown in the attached waveform, Q1’s Vgs drops as Q3’s Vgs rises, suggesting some internal interaction or current sharing between HO1 and HO2 outputs.

The datasheet section 7.3.18 "Gate Driver" states:

“The internal gate drivers support this by sharing the current from the other half bridge, which is switching.”

From this, we infer that CBOOT1 charge might be shared between Q1 and Q3 under certain conditions.

Could you confirm whether such simultaneous gate activity (and possible interaction) between HO1 and HO2 is expected behavior as per the IC's internal design?

If this behavior is by design, we would appreciate it if you could share any available internal details (e.g., driver coupling, internal charge sharing mechanism, or protection behavior) that explain how this occurs during short-circuit or abnormal conditions.

[Question 2]

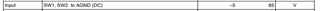

In the Absolute Maximum Ratings table (Section 5.1), the following is noted:

SW1, SW2 to AGND: –0.3V to 65V (DC)

Could you clarify whether “(DC)” refers to a rating under steady-state (non-transient) conditions, excluding voltage spikes or noise?

Also, for parameters such as HB1 to SW1 or CSA/CSB, which do not carry a “(DC)” notation—

should we consider transient spikes included in the absolute max voltage range for those pins?

Thanks,

Conor