Other Parts Discussed in Thread: TPS25751

Tool/software:

Hi team:

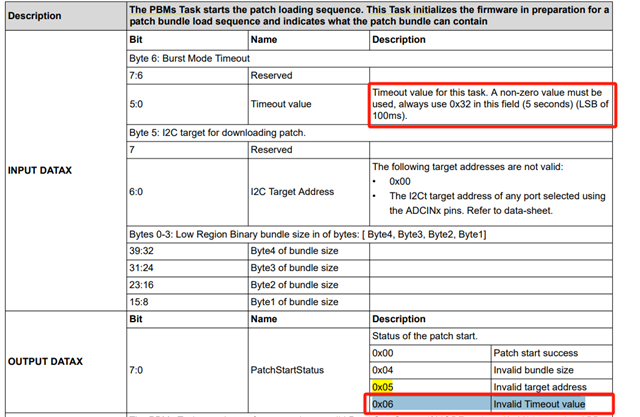

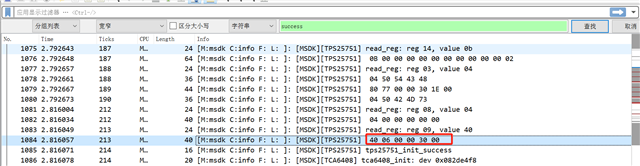

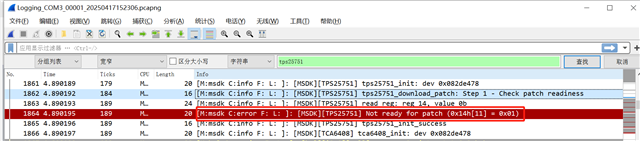

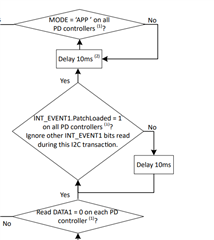

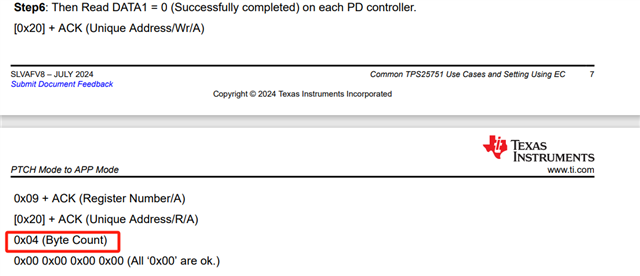

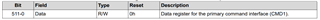

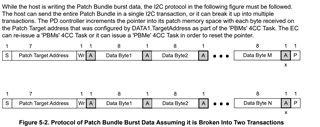

I encountered an error while downloading the patch bundle. When executing step six to read the 0x09 register, it should have returned 0x00 for all, but mine is not. The first number I returned was 0x06. According to the datasheet, 0x06 represents the invalid timeout value, but the timeout value is indicated in the datasheet to be set to 0x32, which makes me confused. I would like to ask what the timeout value should be defined as?