Other Parts Discussed in Thread: AM6442,

Tool/software:

Greetings from VVDN Technologies.

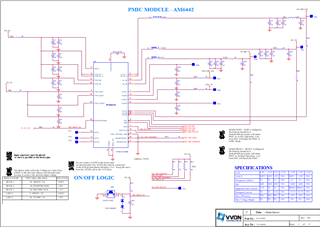

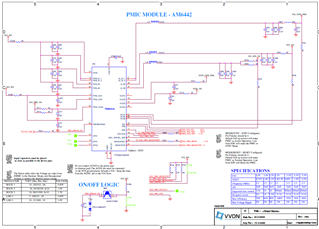

PMIC Details:

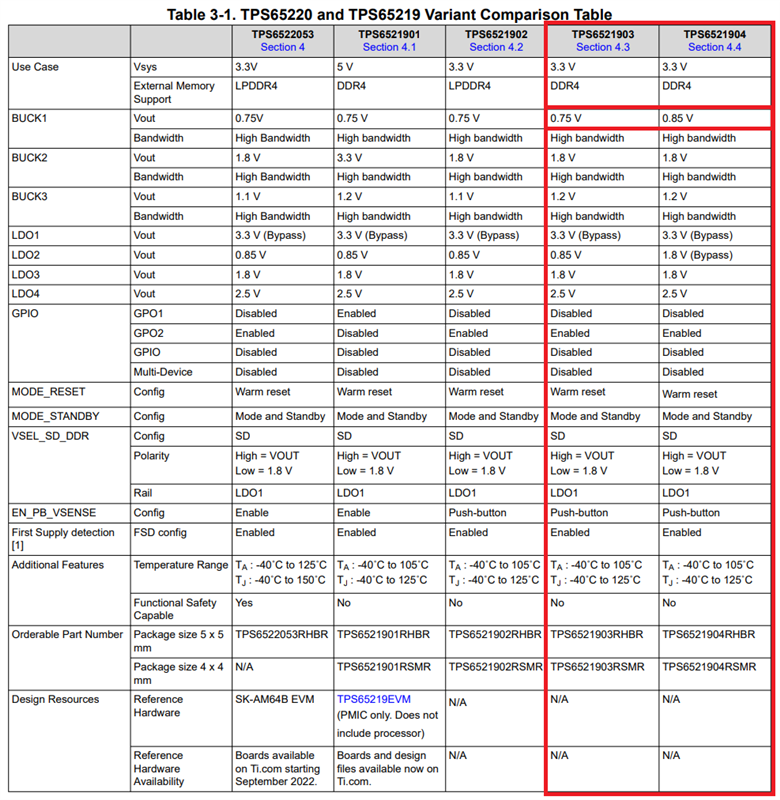

MPN - PTPS6521903RHBR

Desc - IC, TPS65219, PMIC, 7 Outputs, 3-DC/DC & 4-LDOs, VQFN-32

Please find the below attached schematics of PMIC and Provide your valuable feedback.

With Best Regards,

Teja.