Other Parts Discussed in Thread: TPD2S300, TPD4S311A,

Tool/software:

Hello Team,

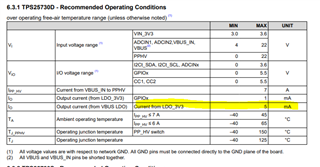

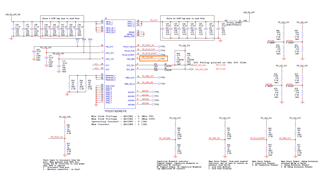

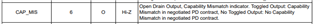

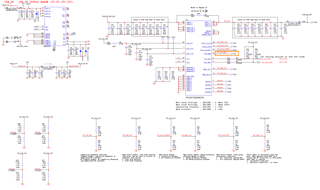

I our design we are planning to implement TPS25730DREFR IC in our design for Sink only PD application (NO BATTERY, Only Plug and Play application with indication over the GPIO of the IC) used in the device.

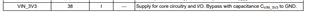

I would Like to know about Purpose of VIN_3V3 Pin !

In our device We are not going to use any Battery .It would be just Plug and Play application.

If we leave VIN_3V3 pin unused/Floating would there be any impact ?

Regards,

Tirthal Patel