Other Parts Discussed in Thread: LM5171

Tool/software:

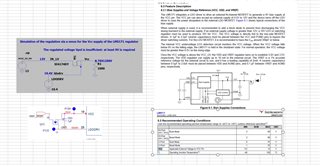

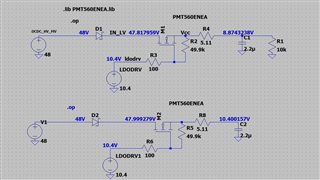

I'm observing oscillations on the Vset pin of the LM5171 circuit depending on the average level I set on this pin: when the level is below 1.5 V, bulk mode works perfectly and the regulation is correct. However, above 1.5 V on the Vset pin, I start to observe oscillations on this input and, consequently, on the LV output.

I suspect there are value errors on some components. Which components are sensitive in the regulation feedback loop? For my design, I followed the advice provided in the spreadsheet "LM5171 Buck or Boost Quickstart Tool_1.0.1.xlsx".

In my design, the Vset voltage is fine-tuned using a DAC coupled by a 100k resistor to the voltage divider connected across the Vref voltage.

Here are some questions:

- What happens when the chopping inductance value is very high? Can a high inductance value cause unstable regulation?

- I limited the peak current by setting the IPK pin to 0.4 V. Could this setting be causing the regulation instability?

Attached are the settings used.

2548.LM5171 Buck or Boost Quickstart Tool_1.0.1.xlsx

Thanks in advance for your help

Regards,

Bruno

.

Hello,

Hello,