Other Parts Discussed in Thread: UCC25660,

Tool/software:

Hi Sir,

When will TI release the simulation model of UCC25660 and UCC25661?

Thanks.

HI Marco,

This is actually the UCC256612 model. High voltage startup is not a feature as the model tries to focus on startup an operation over the full load range. We are working on updating this and releasing versions covering the different options available.

Hi Dhananjay,

The Simplis model requires the SImplis simulation tool. It can't work in Tina.

The LLC topology is far too complex for a pspice based model. If we did make one, it would take forever to run. Simplis is a piece-wise linear simulator that works much faster.

Hi Sir,

Please refer below picture,

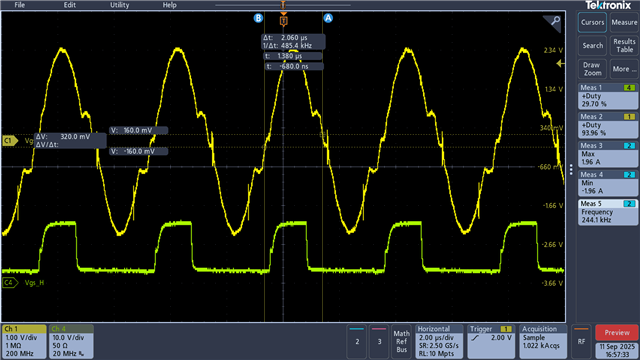

Ch1: Low side mosfet Vgs, Ch2: High side mosfet Vgs,

Could you help check what the Reason the effective duty cycle is to small?

I also upload excel file for the parameter of ucc256612.

Hi Jchk,

Please refer to the attachment, where Lr= 30uH, Lm=300uH and Cr:4.7nF+4.7nF, these parameters are fixed.

Thanks.

/cfs-file/__key/communityserver-discussions-components-files/196/LLC_5F00_TI.pdf

Hi Jchk,

Vin:400V, Out:50V/4A Steady-state.

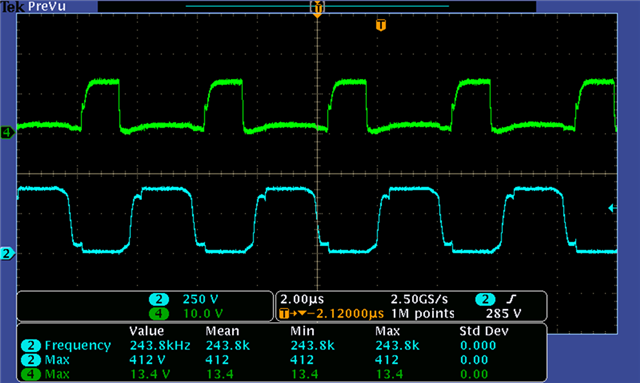

Picture1: CH2: High side VGS, CH4: High side VDS

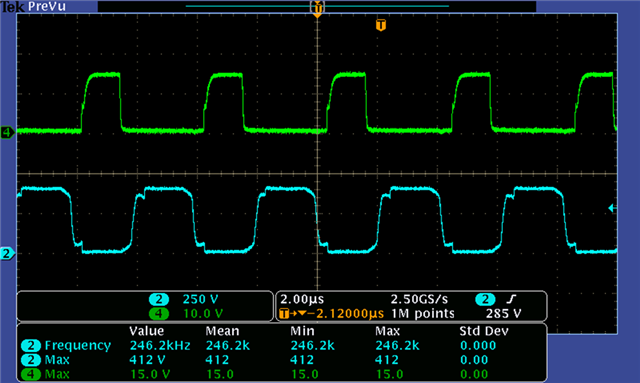

Picture2:CH2: Low side VGS, CH4: Low side VDS

the pulse width is around: 1.2us

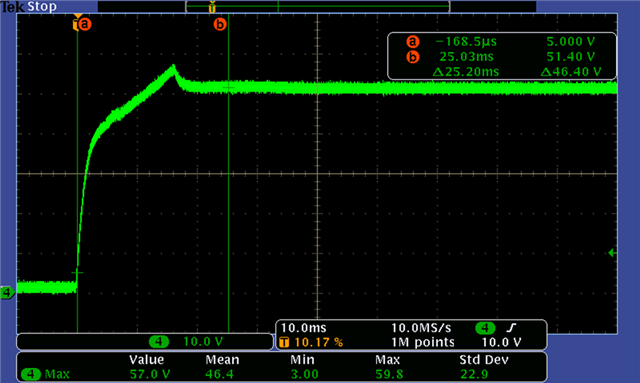

And I also find the overshoot on the Vout, could you help to check?

Hi Jchk,

In the picture, the duty cycle is only 1.2 µs at 243.8 kHz, which means the duty cycle is around 30%.

Could you explain the reason and please provide the simulation results? I couldn’t reproduce the real test result in my simulation.

The capacitor was 186uF, I increased it to 500uF, but it didn't help much with the overshoot.

Thanks.

Hi Jchk,

I understood, as we discussed early

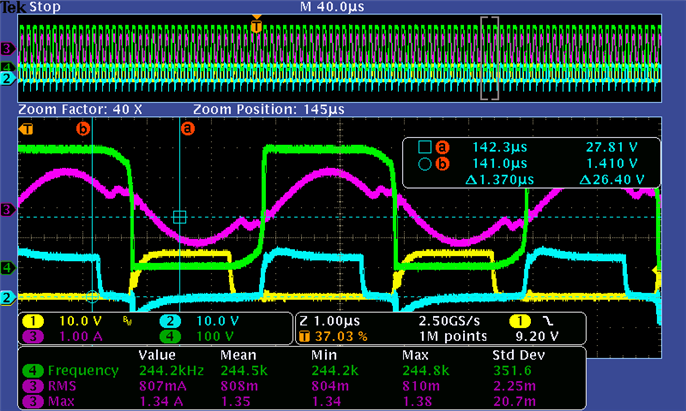

Ch1: Low side mosfet Vgs (Ho), Ch2: High side mosfet Vgs(Lo),

The duty is around 30%~40% @ Vin:400V, Out:50V/4A Steady-state.

So, the duty cycle is small, but I don't know the reason.

HI Marco,

The LO and HO pulses are on for the same duration which is normal and required for resonance. What you are looking at is the dead-time which is required to allow the current in the resonant tank to reverse so the next switching cycle can be ZVS (Zero-Voltage Switched).

Does this make sense?

Hi Jchk, JCHK

This is exactly what I'm curious about — why is the dead-time so large?

How can I verify whether the dead-time value is correct?

I’d like to reduce the dead-time because the duty cycle is too small, which leads to low voltage utilization and prevents the LLC from operating at the expected resonant frequency.

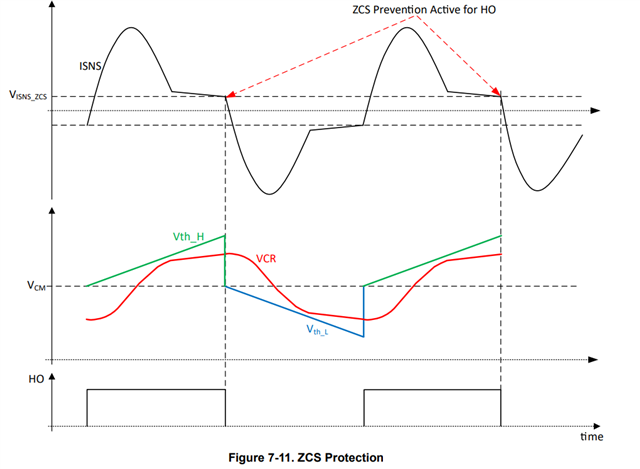

Initially, I thought the smaller duty cycle was caused by the ZCS protection feature, but based on actual measurements, that doesn’t seem to be the case.

Could you provide more methods to help me confirm whether the duty cycle is indeed too small?

This could be a serious issue in the design.

Yellow color is :V_ISNS

Green color is : VGS of High side mosfet

Thanks.

Hi Marco,

The maximum dead time is 1us. This is the adaptive dead-time is determined by looking a the slew rate on the HS pin. If you are hitting the maximum dead-time it could be that your COSS of the switch stage is too large. See Section 8.2.2.12:

This means your LI2 energy needs to be greater than the COSSV2 energy.

Can you try FETs with a lower COSS to see if it helps?

Regards,

John