Other Parts Discussed in Thread: UCC21710, , UCC15241-Q1

Tool/software:

Hi,

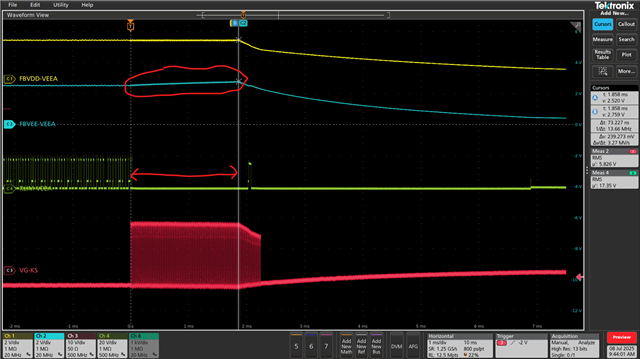

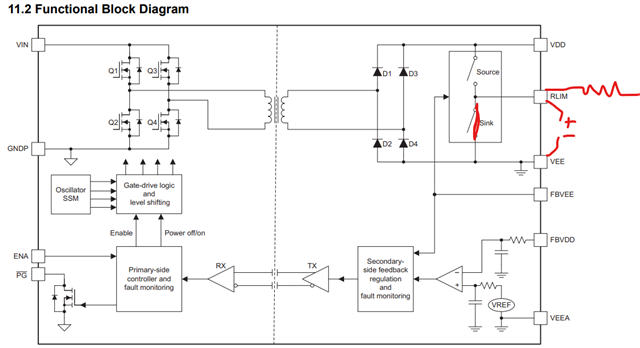

I am using the UCC14241 IC to provide dual output power rails for a SiC MOSFET gate Driver (VDD: +15V; VEE:-5V). The gate driver IC I'm using is UCC21710. Please see the excel design calculator for the UCC14241 attached.

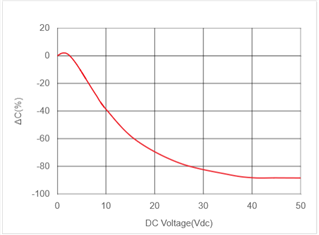

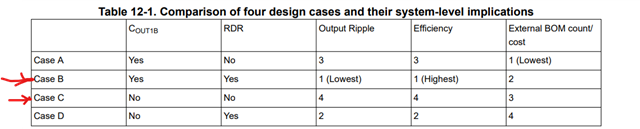

I am trying to determine the correct value of RLIM to use based on the inputs I have provided in the excel calculator. Also note that I am implementing the single RLIM network. I am not using the RDR network.

Also note that I have followed all datasheet layout recommendations for filter capacitors close to UCC14241 and UCC21710 appropriately.

Based on the above scenario and my inputs, the excel calculator suggests using the closest, smaller value to 8.2 kOhms for single RLIM.

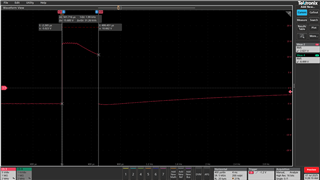

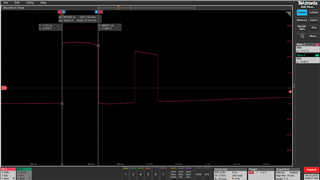

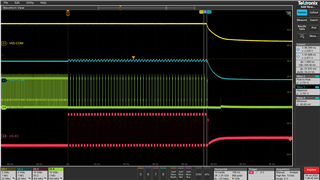

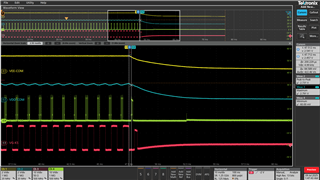

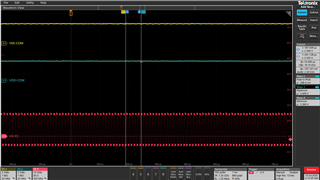

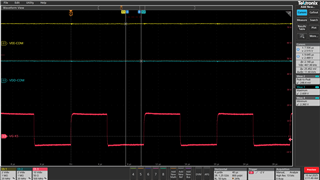

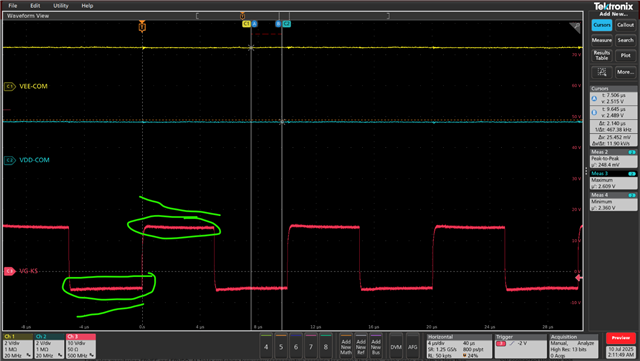

In my PCB implementation, I tested the UCC14241 circuit with 6.2 kOhms and 8.2 kOhms. However, the VDD and VEE measured from UCC14241 are 0V and it seems to be in a fault state.

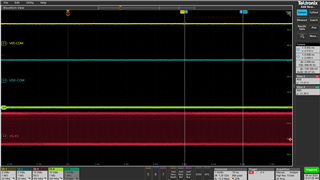

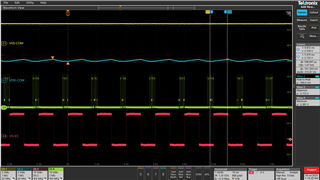

I then changed the RLIM to 1 kOhms, and it works. I am measuring +15V and -5V for VDD and VEE, as expected. This test was performed under light/no load conditions: UCC21710 is enable but PWM inputs are held low.

So, this is my question:

What is the maximum single RLIM I should use to minimize dissipation of UCC14241? I also want to ensure that the VDD and VEE regulation is good with 100 kHz switching frequency when gate driver is operational.