Tool/software:

Hi,

I have a design where the devices fail to some sort of internal short circuit after either intermittent power connections to 24V or prolonged operation (>20mins) on 24V. The failure rate is at 100%.

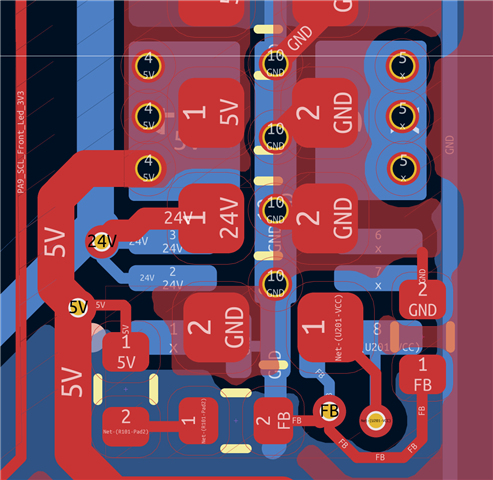

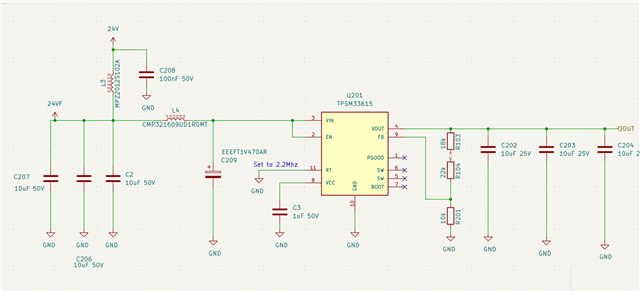

I have already build two versions of the board, the first one one without input PI filter (just 30uF X7R), the other one with the filter shown below. I think the layout is reasonable though, as always, it could be improved.

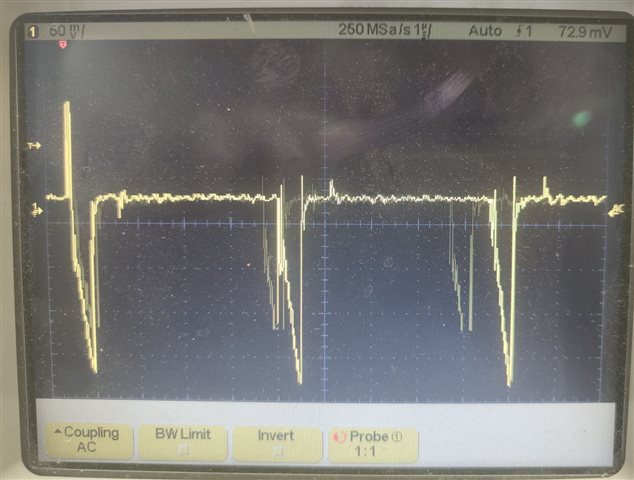

I checked for regulation oscillations, load step responses with a 200MHz scope and they look all nice and clean. I read

Power consumption is at 5V/40mA typically without any load spikes. The device stays cool. With this input filter, the ripple at the devices input is quite noticeable as can be seen in the screenshot.

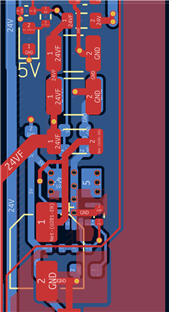

I also tried to shorten the line to the 1uF Vcc cap. See below. Didn't help either.

Do you see any hint on why the devices fail? A quick response would be fine as we cannot reasonably test this design iteration due to this problem.

Input voltage With pi filter Vin=28V, Vout=5V, load 40mA.

Manual addition of a 2nd 1uF Cap at VCC with shorter lines.