Other Parts Discussed in Thread: LM5143-Q1

Tool/software:

I have several questions regarding the LM5143A-Q1 in our application:

- High-Side MOSFET Overheating

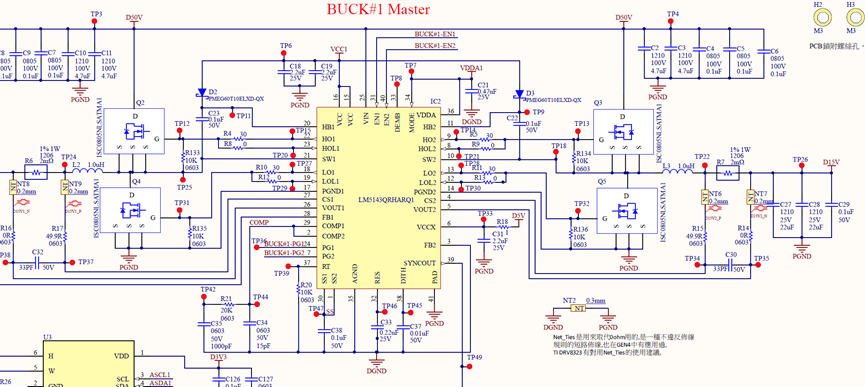

We are using a two-phase synchronous buck converter with an input voltage of 25 V, output voltage of 15 V, and a load current of 23 A. The high-side MOSFET temperature (ISC0805NLSATMA1, gate resistor changed to 7.5 Ω) reaches 140 °C. What countermeasures can be implemented to further increase the output current to 35 A?

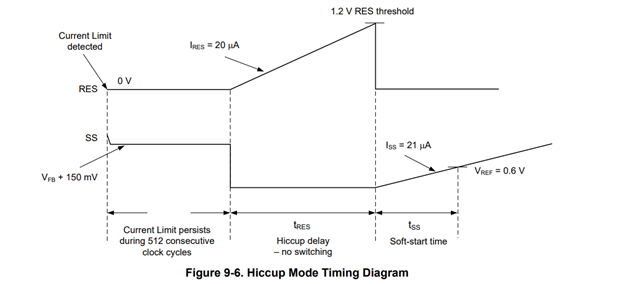

2. Sawtooth Output Voltage & RES Pin Pulses

If the output voltage exhibits a sawtooth switching waveform, the RES pin outputs pulses, and VDDA outputs 5 V, what could be the cause of this behavior? How can this abnormal condition be resolved?

3. Determining Fault or Protection Mode

How can we determine whether the LM5143A-Q1 is faulty or has entered a protection mode?

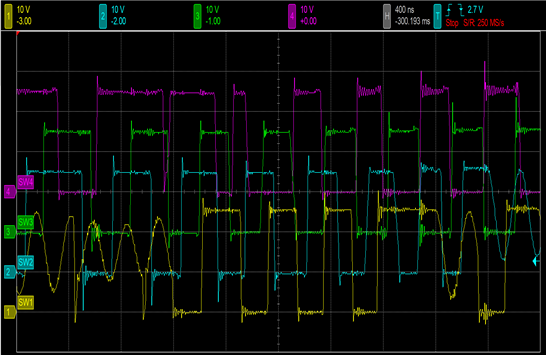

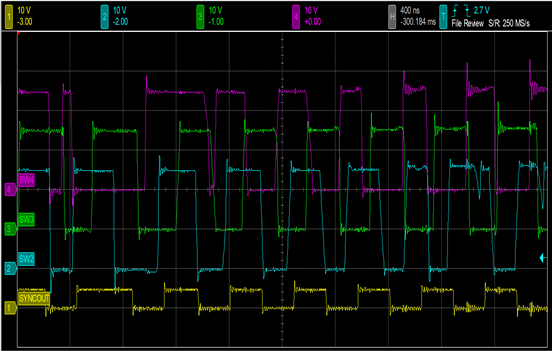

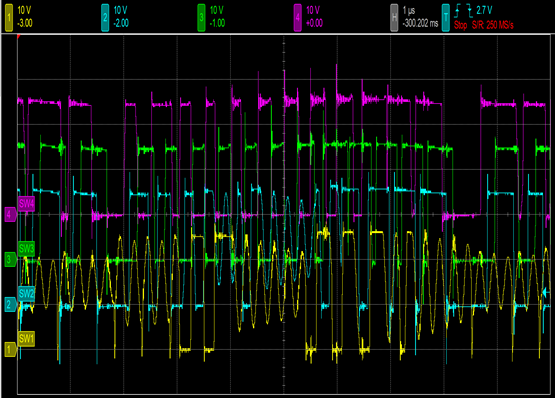

4. 4-Phase Synchronization Issue

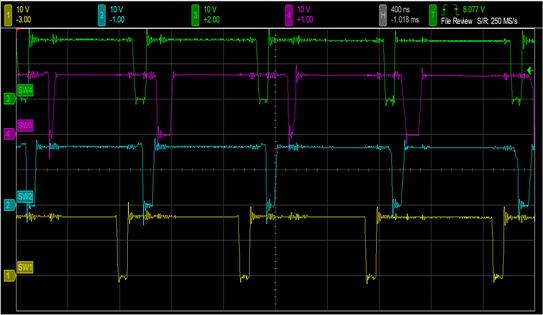

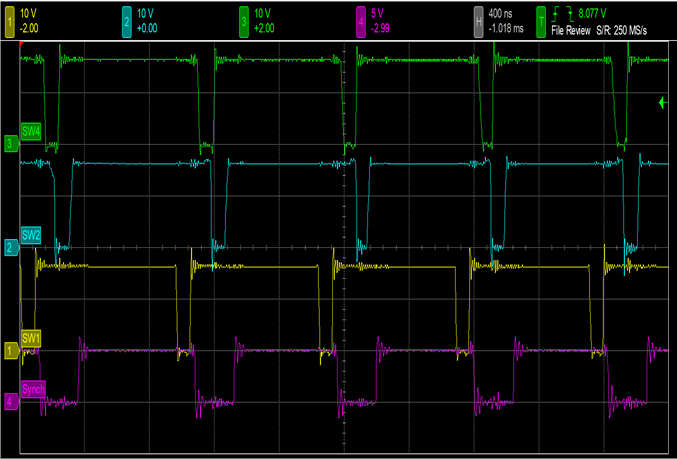

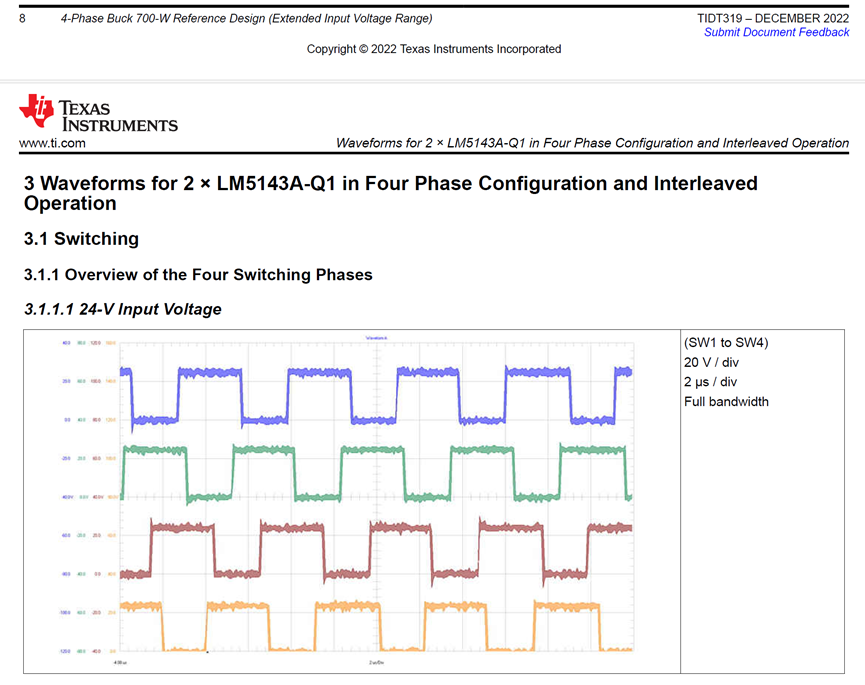

We are using two LM5143A-Q1 devices to achieve a 4-phase synchronous buck configuration. Input voltage is 25 V, output voltage is 15 V, and there is no load. To verify the 4-phase synchronization, we measured CH1_SW1–PGND, CH2_SW2–PGND, CH3_SW3–PGND, and CH4_SW4–PGND. The CH4_SW4–PGND waveform does not match expectations (we expected SW3 to lead SW4). Measuring CH4_SYNCOUT (same as CH4 waveform) relative to SW1, SW2, and SW4 shows that the phases are not in the expected 90°, 180°, 270°, and 360° sequence. The ideal waveform should match the reference waveform in the TI documentation.

Could you please help us analyze these issues and suggest possible solutions?

Thank you for your support.

Best regards,

YUMING