Other Parts Discussed in Thread: INA293, INA187

Tool/software:

Hi Ulrich,

Regarding my previous question which is now locked, we've finally had time to do more testing on our system and upon doing more detailed testing we noticed some things that we think might be unusual.

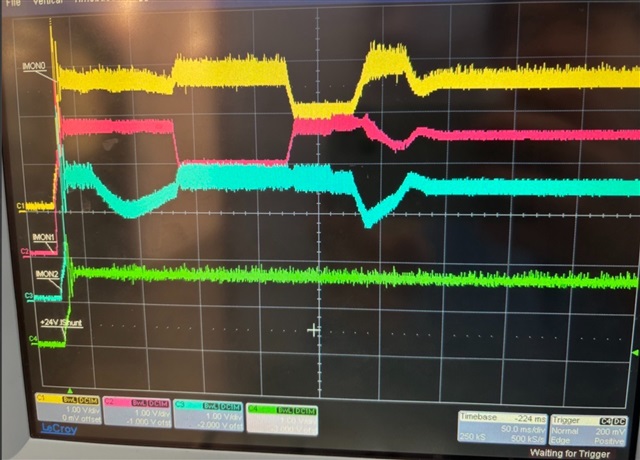

1)The time for each of the individual channel's current to settle into steady state is very long, >50x the voltage settling time. Voltage settles in approximately 7ms but current of the individual channels settle roughly after 350ms regardless of the size of the current step change.

2)The current sharing stabilizes in what we think might be an unusual manner. After the initial section that looks like an underdamped oscillation (approx the first 10ms or so), until the currents reach steady state it looks more like some sort of a piecewise function.

3)All this behavior is seen with 2,3, and 4 power supplies enabled

4)I should note we are using a low side current shunt with an INA293A2IDBVR between the shunt resistor and the CS+ inputs to improve handling of negative inputs beyond the -0.3V specified in the UCC29002 datasheet.

The attached image shows 3 of the 4 CSO lines (IMON0-2 in the image) and the 4th trace is the high side shunt prior to the electronic load (sum of all 4 supplies). While not shown, voltage stabilizes within 7ms of the initial rising edge and the 4th CSO line behaves similarly to the ones shown. Please ignore the large amount of noise that can be seen on the CSO line traces as we've proven that that is a measurement artifact

Is this all expected behavior? Also how can we improve the response time to reach steady state? My concern is that under heavy load, the duration of time where the currents are unbalanced is potentially long enough for one of my supplies to trip over current protection.