Tool/software:

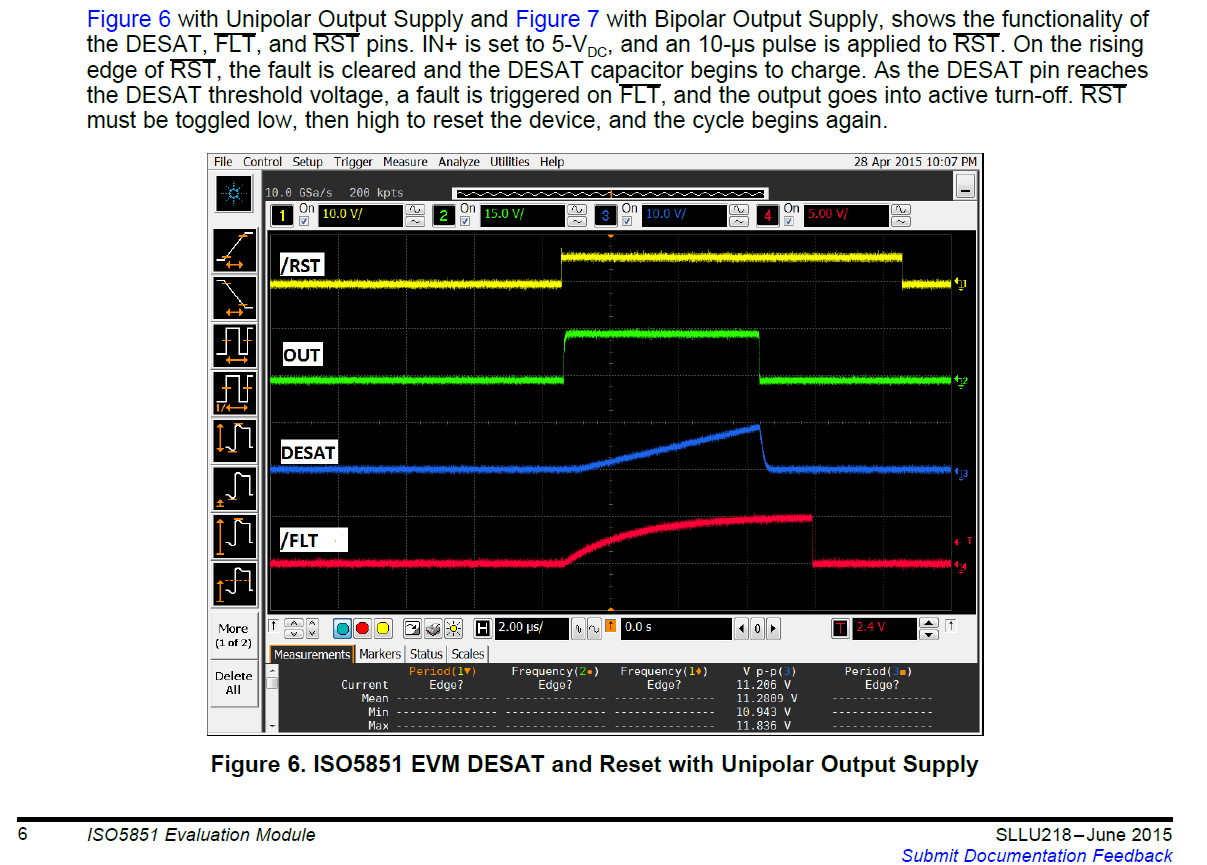

Fig. 6 of sllu218 "ISO5851 Evaluation Module" User's Guide (see below) did not explain how the DESAT waveforms are generated in this ISO5851 Evaluation Board & how it is implemented,

The related original detailed test procedures must have been kept in the related test report,

not sure if related DESAT related test component & schematic & steps can be shared with me, so we can know how it is implemented exactly to get the related Fig. 6 waveform?

this kind of information will be able to help customers who use this ISO5851 evaluation board to follow to do the related DESAT testing.

Thank you and look forward to hearing from TI when convenient.

yenwu lo