Other Parts Discussed in Thread: UCC28951, UCC28950, UCC28950EVM-442

Tool/software:

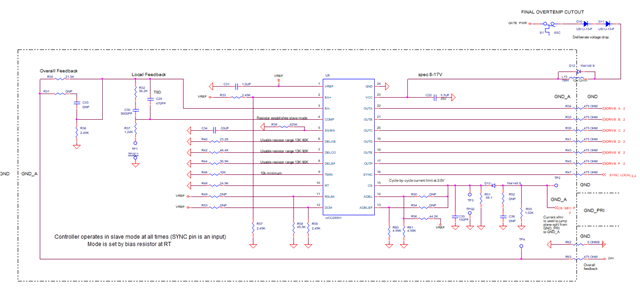

Suspecting improper connections or timing of secondary FET gates as the cause of large current surges that overpower reflected secondary current ramps, I have inspected the connections of all gate drivers (I believe they're OK) and have used SLUC222D to recalculate resistors at DELAB, DELCD, and DELEF. On the CS-feedback side, I have ADELEF connected to ground through 4.99K, and have ADEL connected the same but with 44.2K also connected to VREF. While debugging this destructive current I am running at 25% load and relatively low input power voltage to avoid the need for current scaling. (At full power the bridge FETs only last a few seconds.)

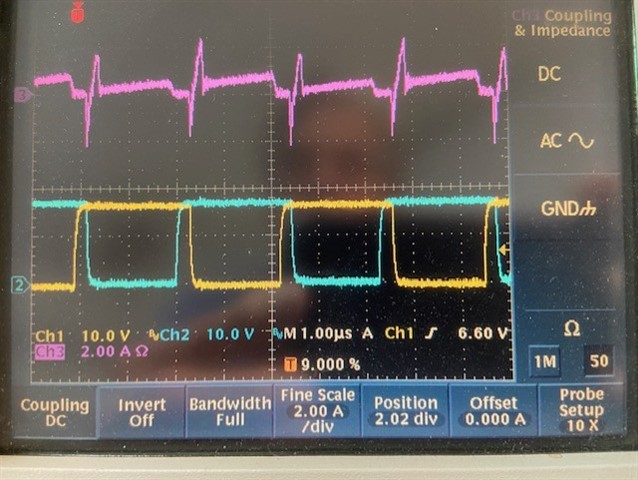

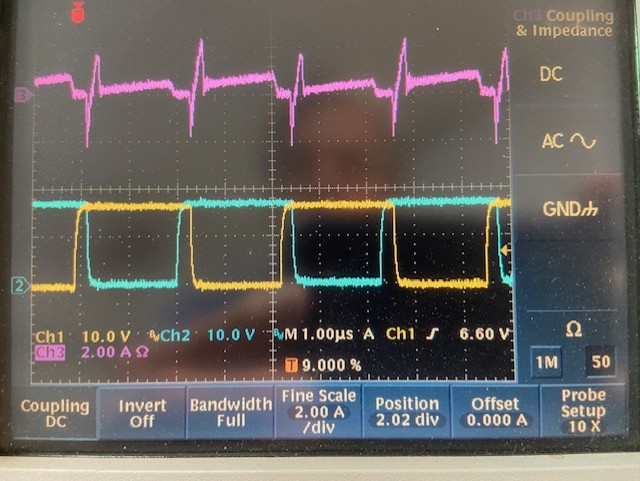

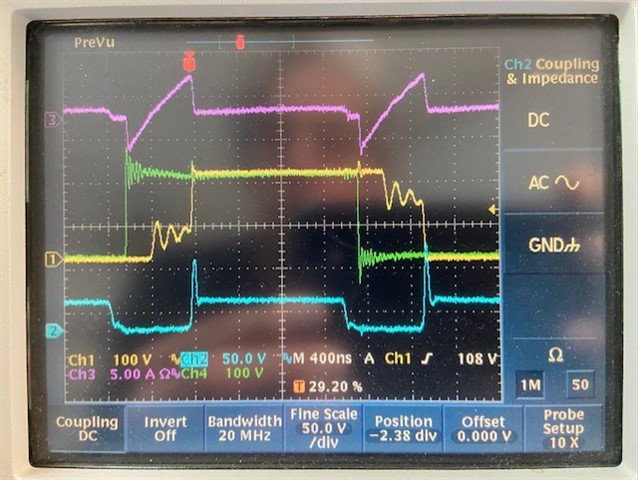

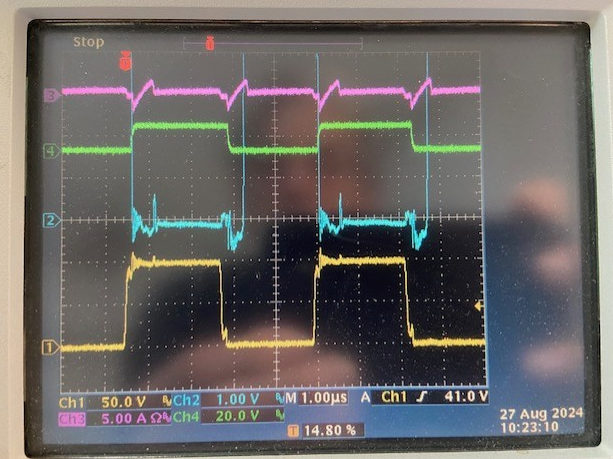

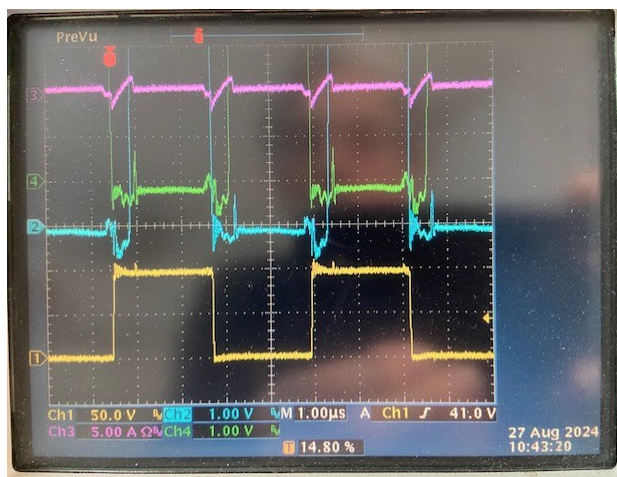

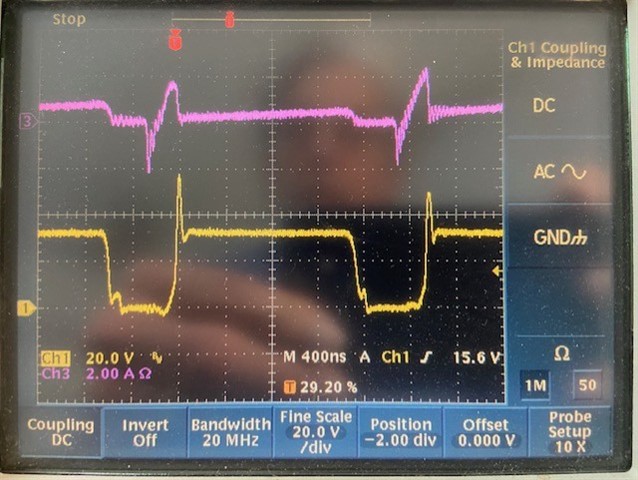

The photo I sent in an earlier post had a misleading trace (magenta,second from top) which I had incorrectly identified as the center tap of the secondary, which it can't have been. But at least it served as an invitation to sketch in what the secondary center tap should have looked like. All photos below are from the delay-adjusted circuit described above. The first photo has just two traces: The upper trace is the power input current, taken at the top of the bridge with a current probe. It still shows the unexpected surge as well as the expected reflected-secondary current ramp. The lower trace is in fact the secondary center tap. Note that the unexpected surge consumes about half the dead time between secondary power pulses and ends precisely at the beginning of the power pulse.

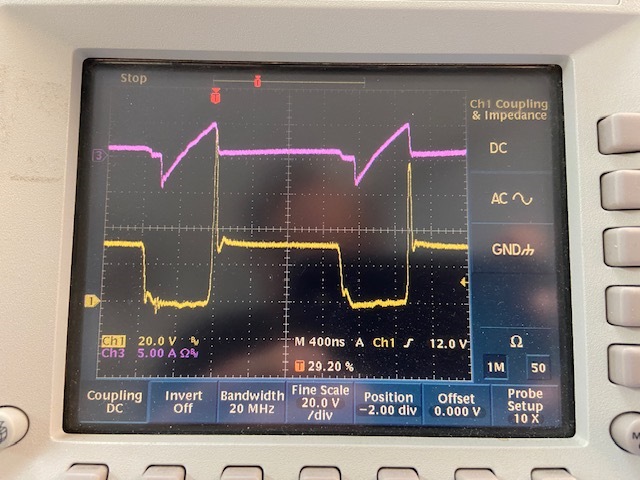

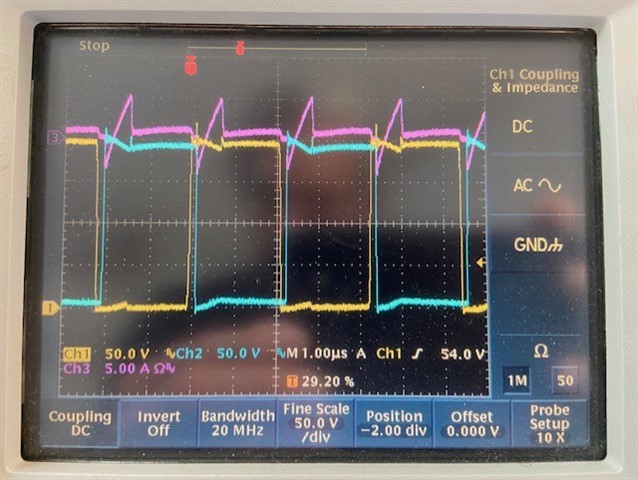

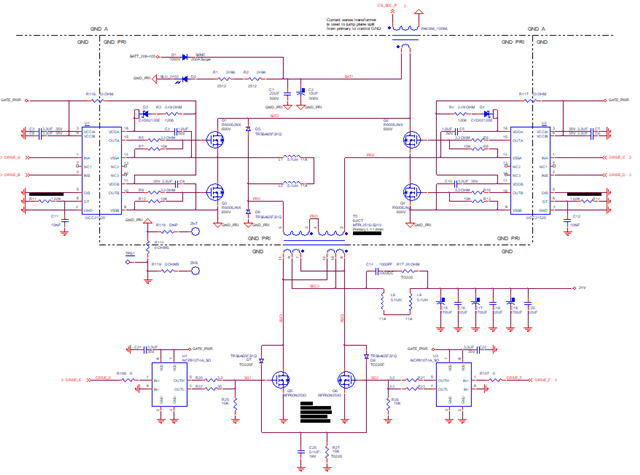

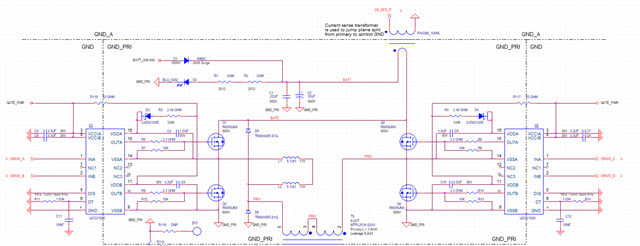

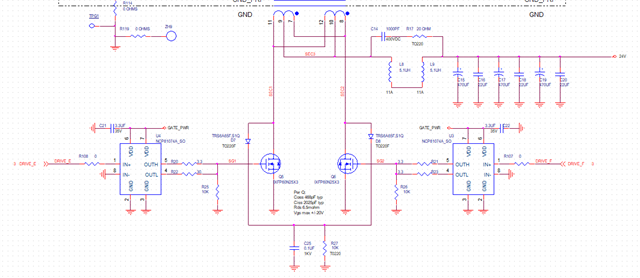

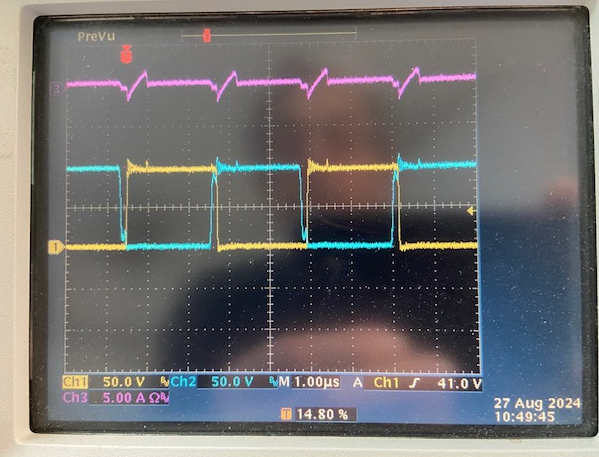

The photo below shows the two ends of the bridge (yellow and green, larger waveforms), and the two secondary gates (blue and magenta, smaller waveforms). Note that the gates signals overlap their corresponding primary signal times, and nearly overlap each other. Is this timing correct?

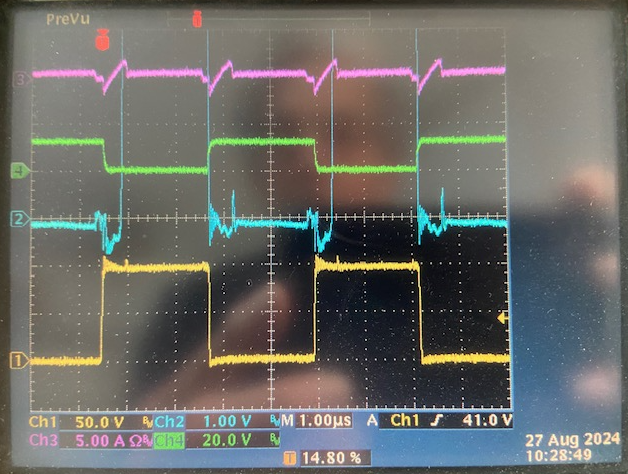

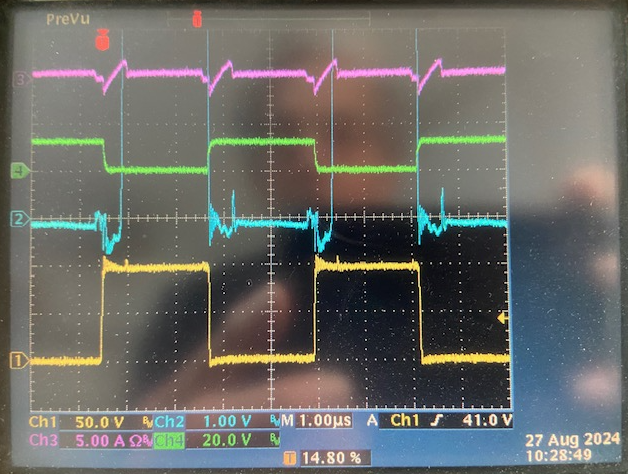

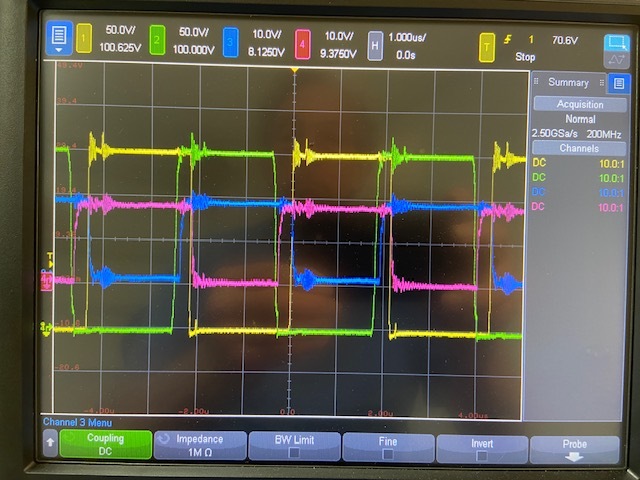

The last photo shows the primary current and the secondary gates. Here it looks like the two secondary gates do overlap. Note the alignment between the current surges and the apparently-overlapping gate signals. Is there a relation between these beyond coincidence? I was surprised to find this overlap. I'm using NCP81074A gate drivers. These have separate rise and fall outputs. Right now the gate resistors are the same and quite small (3.3 ohms). Should I perhaps make the rise resistors substantially larger to try to get some separation between the secondary FET on-times?