Tool/software:

Dear TI Engineer,

When we testing the UCC28070DWR power board, it is normal to output 100W when the low voltage is 110V input. However, when the load is added to 200W, the PF value is only 0.4. Can you help analyze the reason?

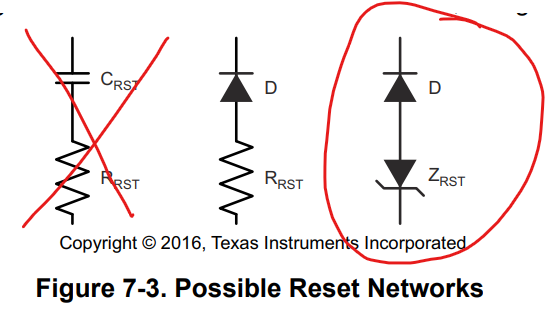

The schematic is as below:

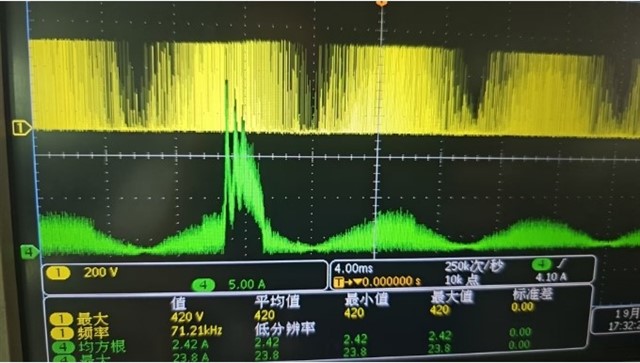

The waveform is as below:

Thanks,

Kind Regards