Tool/software:

Dear TI-Team,

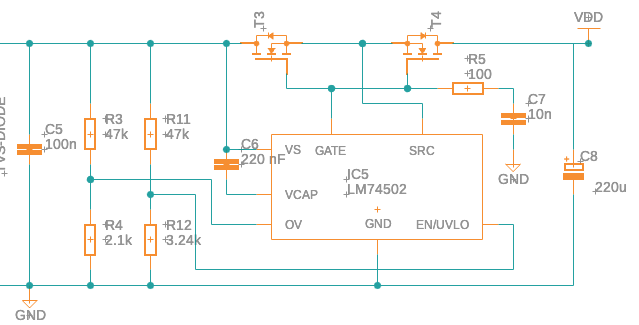

my LM74502 circuit looks pretty similar to figure 9-1 from the datasheet. The MOSFEST are SIR186DP-T1-RE3, same as in the eval board. The circuits looks like this :

:

The overvoltage protection should engage at 29.2V and disengage at 26.7V. Likewise, the undervoltage protection should engage at 17.7V and disengage at 19.2V. Values are nominal values.

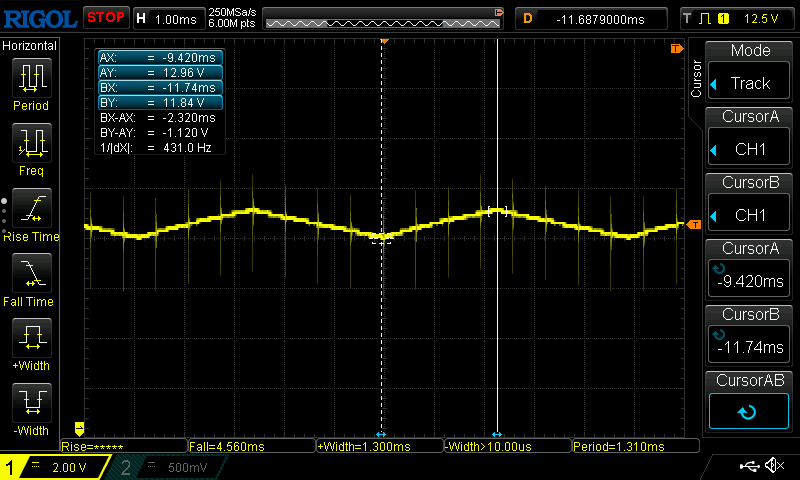

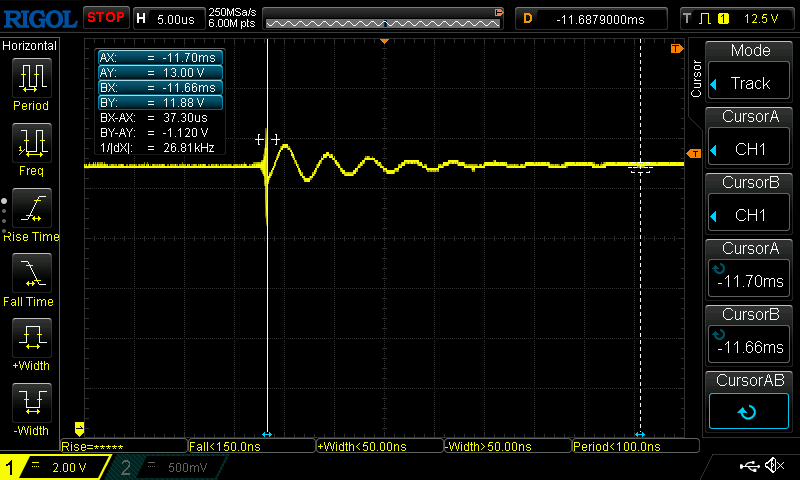

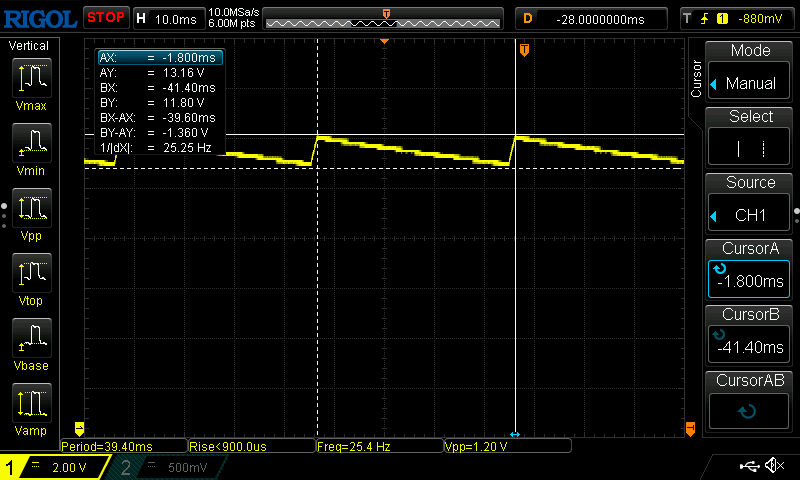

If I power-on the circuit with 24V, which is well within the operational range, the output is only 4.54V and the gate voltage is 6.3V. Once I lower the voltage to 21.2V, the circuit activates fully and brings the output to 21V and the gate voltage to 33.5V. With the circuit working, I verified the ULVO, fall to be 17.5V, ULVO, rise to be 19.0V and OVP, rise to be 28.8V. Now if I reduce the input voltage from 30V, the output voltage rises to 4.54V at 26.7V. It is only when the voltage drops below 21.1V, that the system works normally. Reverse polarity protection works. Also, the circuit works as expected if I start it up with a voltage below 21.1V

What is going on in the voltage range between 26.7V and 21.1V? What is this weired mode where the IC does not fully charge up the gate?

Best

Jan