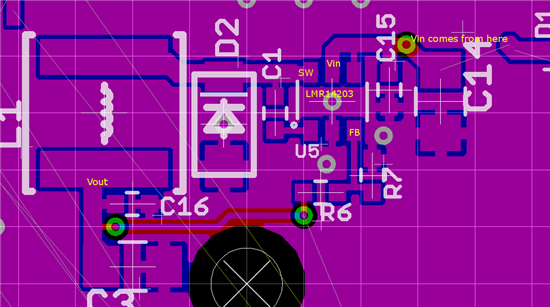

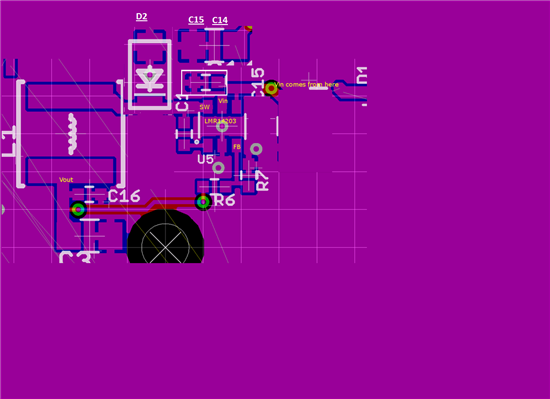

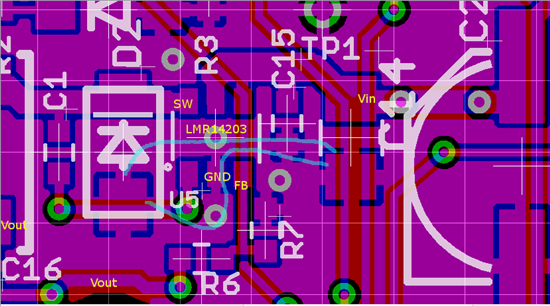

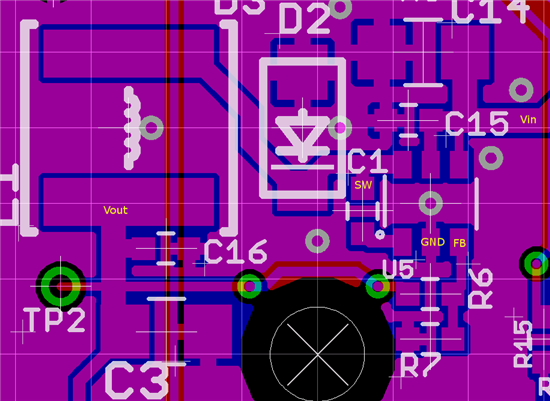

I have a design using the LMR14203 but I only get the desired voltage across the very low end of the Vin range and in that range the diode gets hot.

I am at a loss to explain why the circuit doesn’t work so I am hoping someone can figure it out. This is a very simple circuit but perhaps there is something simple I am missing???

Inputs to WeBench: Vin7-32V, Vout=5.0V, Iout=0.1A, Ta=30C.

5282.LMR14203.docx has details, schematics, layout and scope shots.

The problem is: When Vin is between 5.3V and 6.6V, Vout is 4.6V (but not 5.3V) and the incoming power is drawing 250mA so somewhere the power conversion circuitry is wasting 150mA. When Vin is above 6.6V I only get 0.4V out and the circuit doesn’t work at all. The current from Vin drops to 40mA in this range.