Hi,

I found that the abnormal startup when VIN turn off and on with short interval. Please see following background and give your comment for question.

Background

- The normal startup could be seen when VIN is turned on and off with long interval.

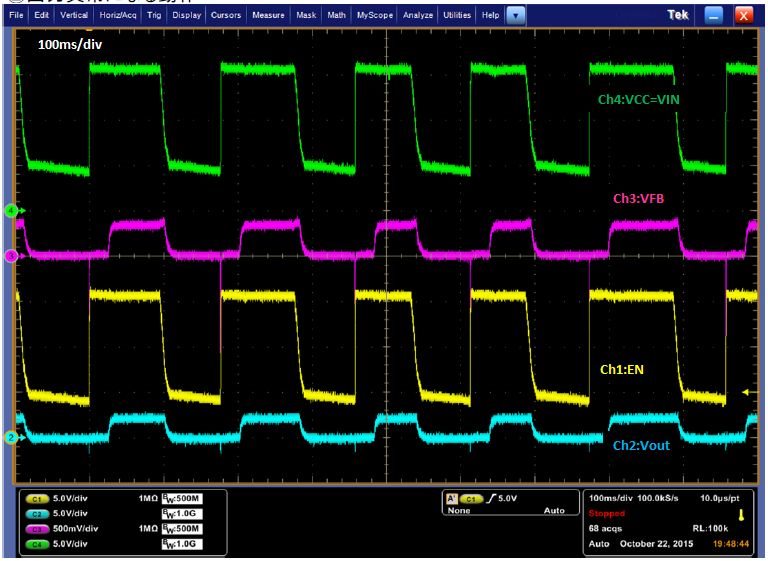

- But the abnormal startup was happened when VIN is turned on and off with short interval.

- I guessed this cause is that the converter was restarted before the VREG5 down below UVLO threshold, so I added zener diode between VIN and VCC to keep VCC lower than VIN. See page 2 ow attached.

- Then I could resolve this abnormal startup issue.

Question

- Can you please give your comment for the cause of this abnormal startup issue?

- Can you recommend this workaround that add zener between VIN and VCC? Please let me know if you have better workaround.

Your comment will be appreciated.

Best Regards,

Sonoki / Japan Disty