Hello,

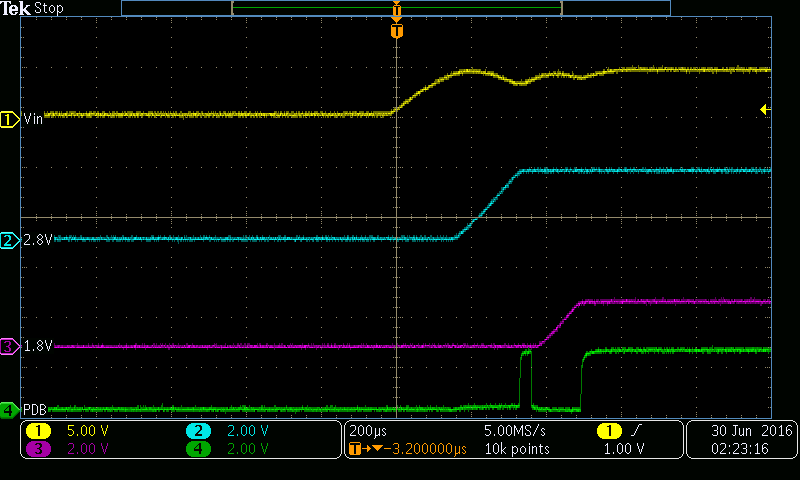

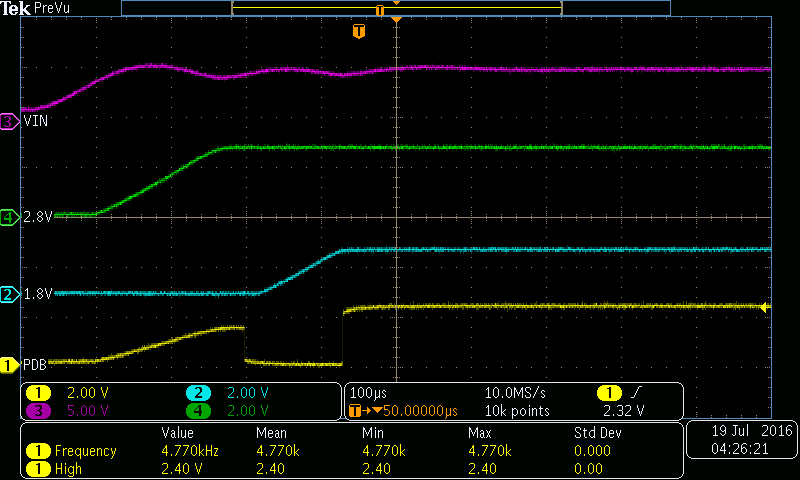

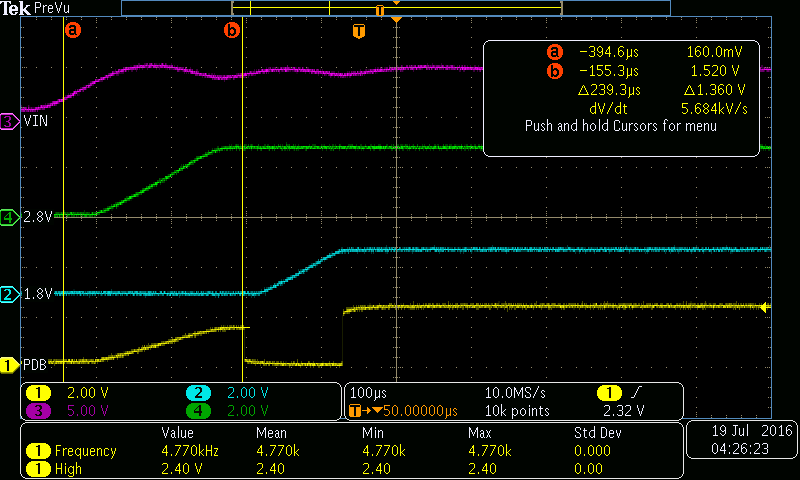

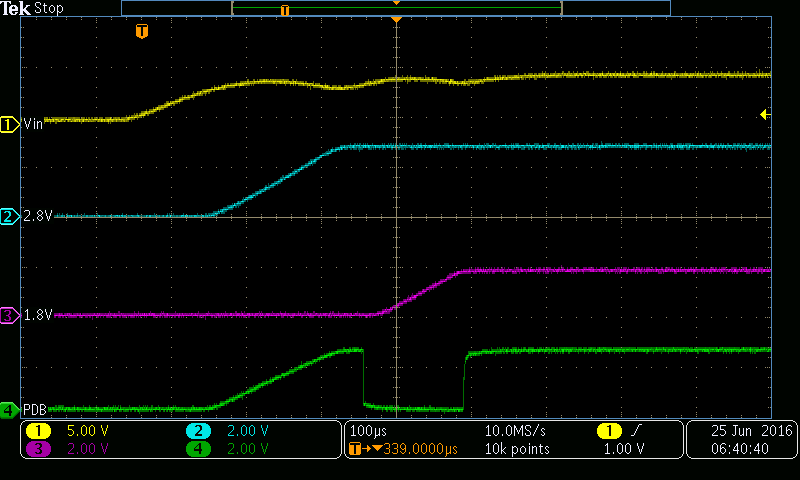

I am seeing an unexpected ramp and drop on the Power Good node of the TPS62171, which controls a RESET pin of a serializer. This PG output must be pulled up to 2.8V for a valid logic HIGH on a serializer, and the output of the '171 is of course 1.8V. I am currently using a 100kOhm pull-up resistor.

I need the 2.8V rail to come on before the 1.8V rail, and the serializer to come out of reset once the 1.8V has stabilized.

What happens is, when the 2.8V rail comes up, this Power Good tracks it, then drops to 0V, then steps up to 2.8V once the 1.8V output has reached its threshold.

However, when I pull the Power Good output up to 1.8V, (not reaching the valid logic HIGH threshold for the serializer RESET), this does not happen, but as I mentioned, the serializer does not come out of reset.

I've attached the schematic which shows the Power Good being pulled up to 1.8V, and the sequencing waveforms.

Please let me know if more information is needed.TIDA-01002 Preliminary Schematic.pdf

PDB is the same node as PG.