Hello to all,

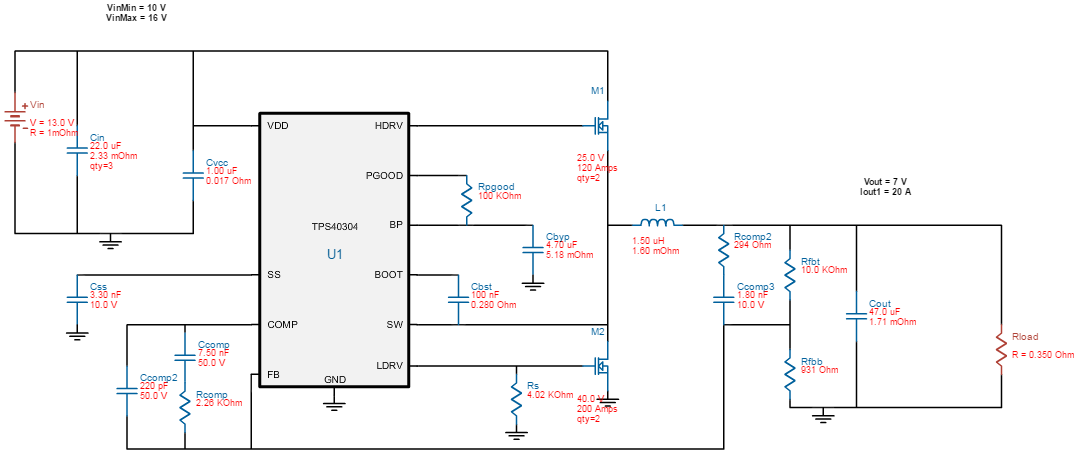

For couple of days I am trying to start that TPS40304, but still no success. I need your ideas and help, so I hope my post wouldnt be ignored :). The initial design is from WEBENCH, but I think it is not correct in some way, as the schematics isn ot working...

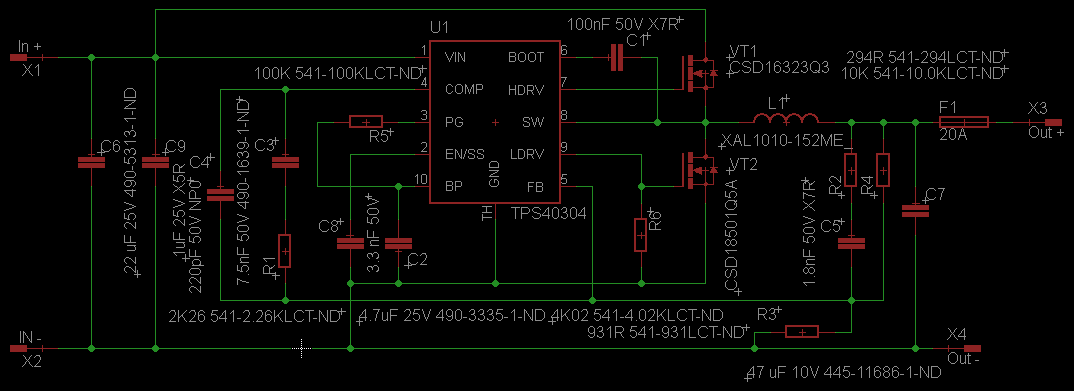

Everything was transfered to Cadsoft Eagle:

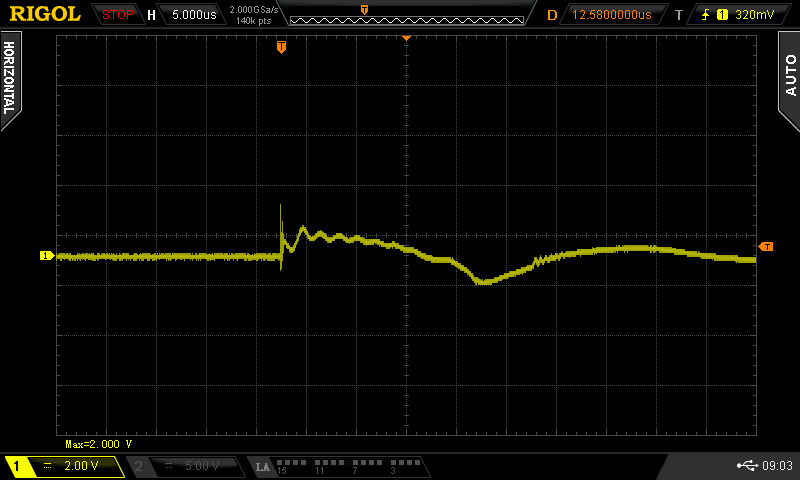

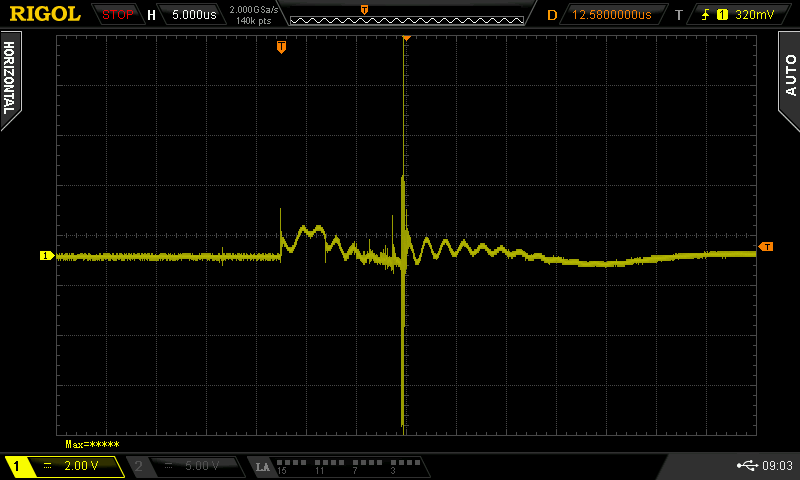

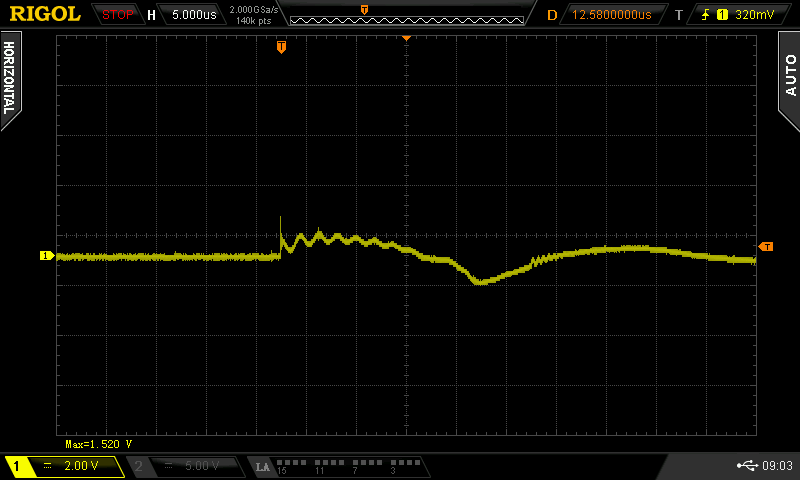

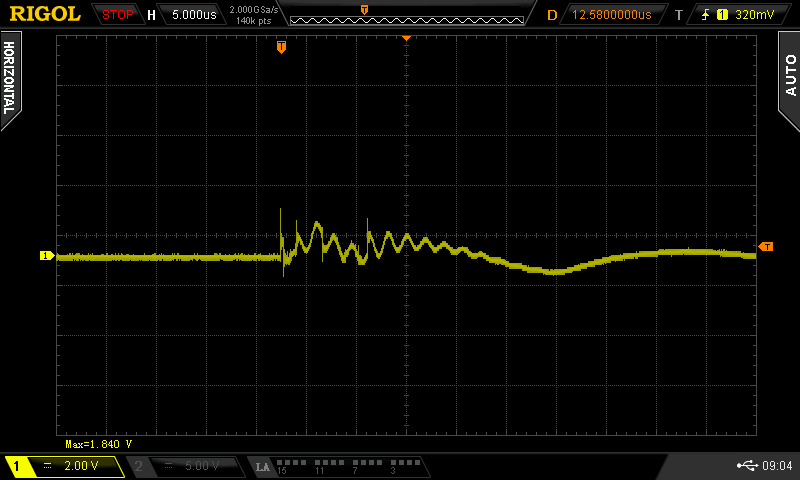

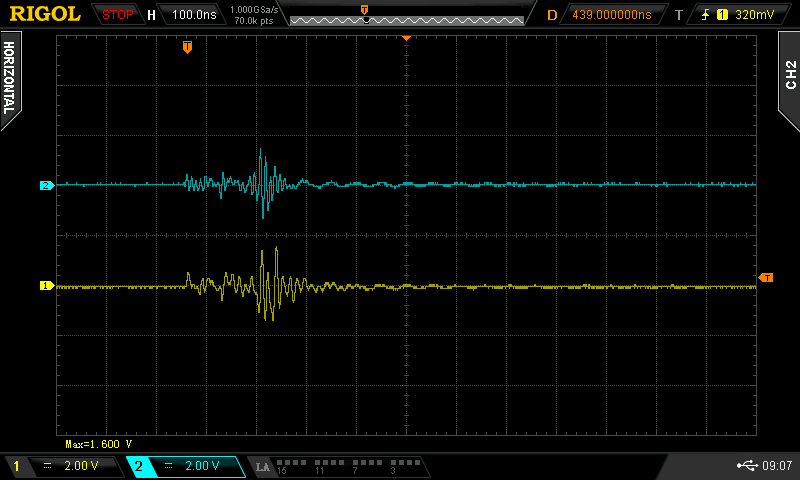

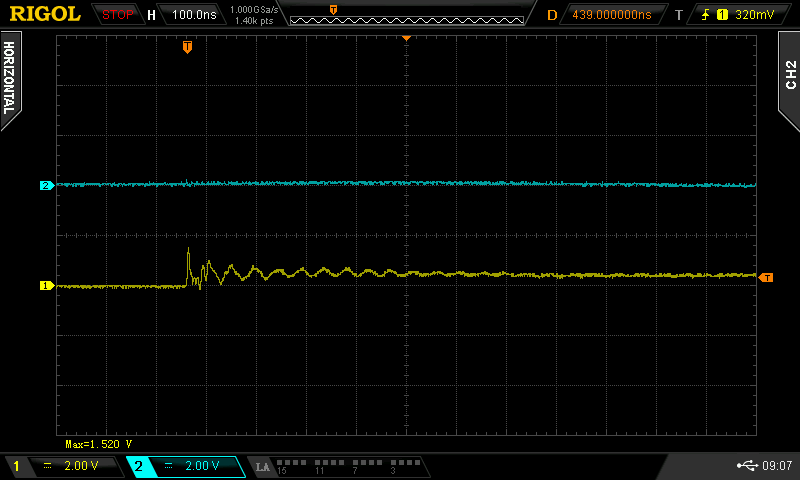

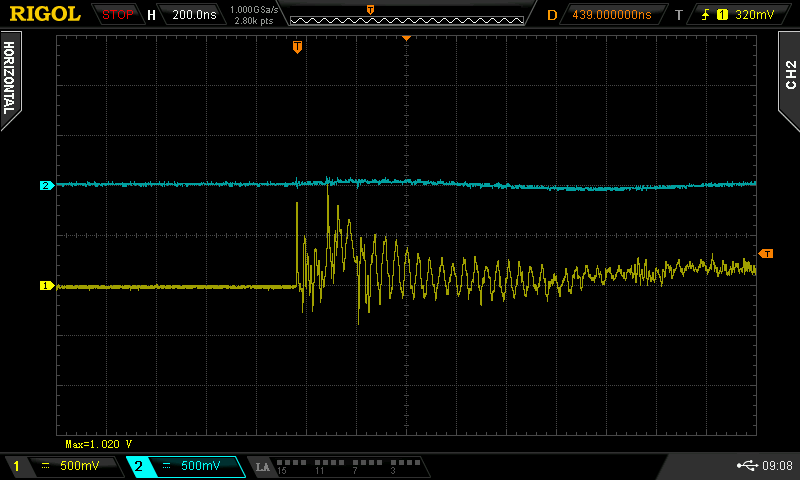

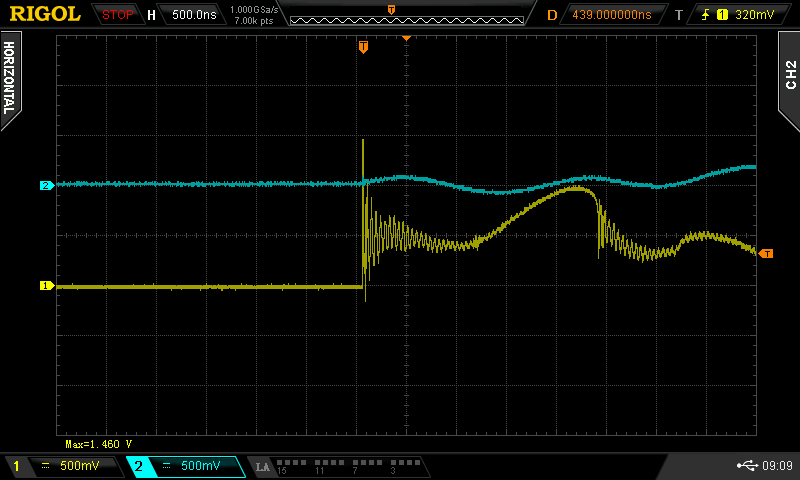

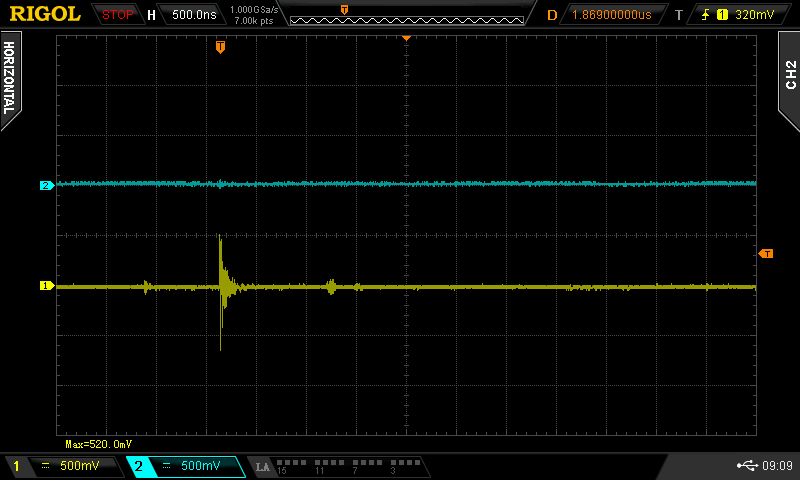

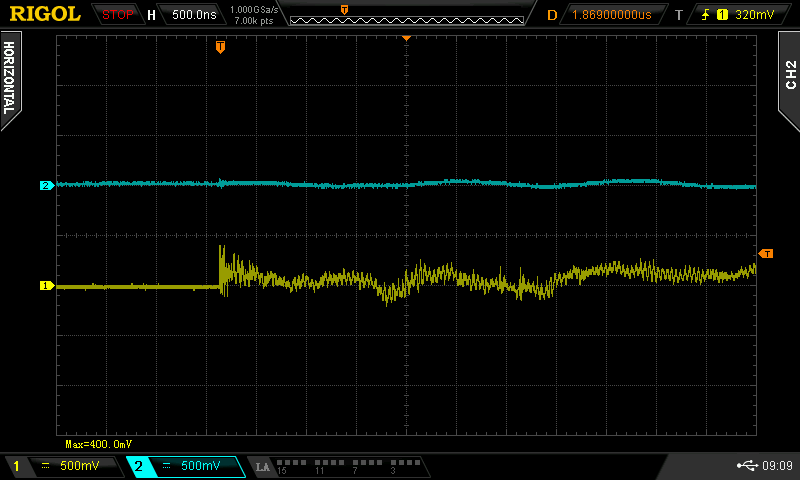

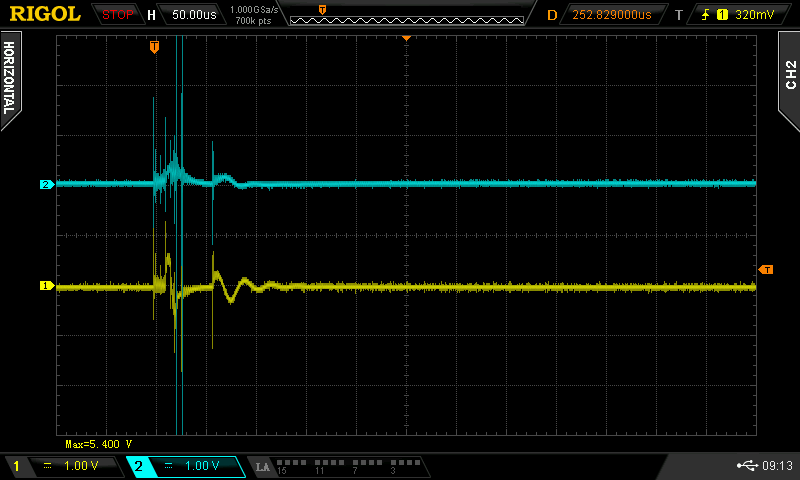

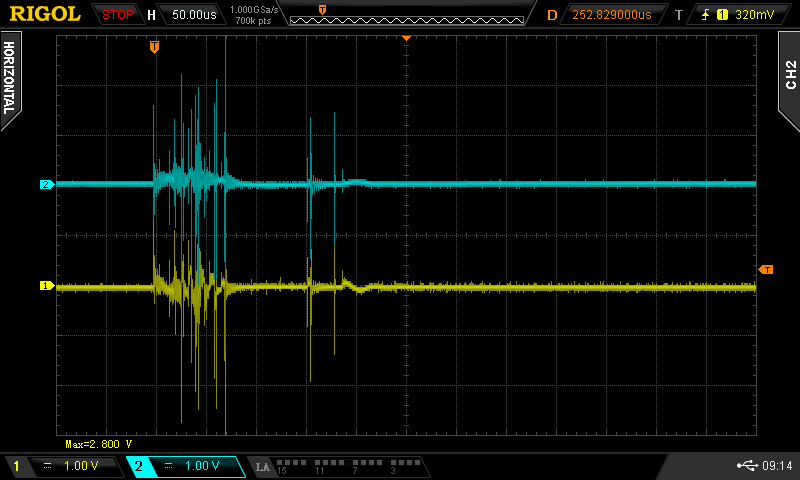

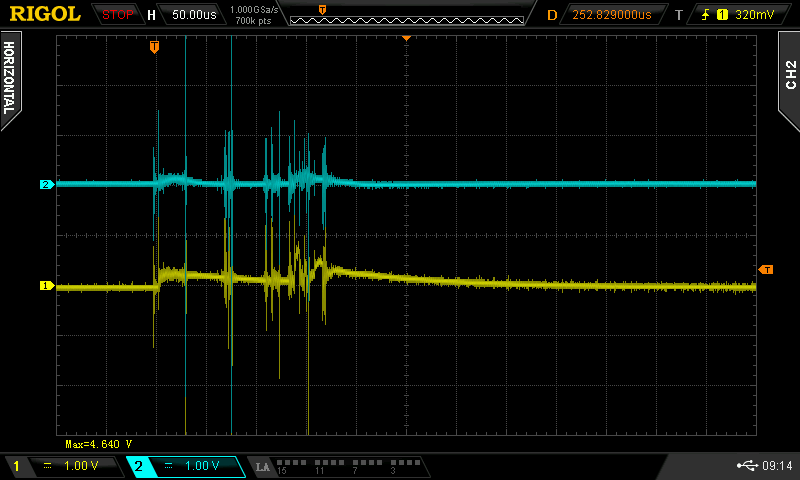

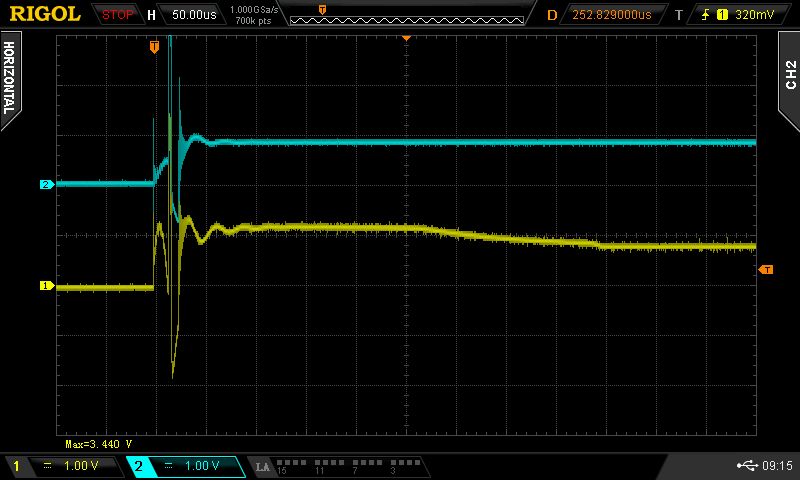

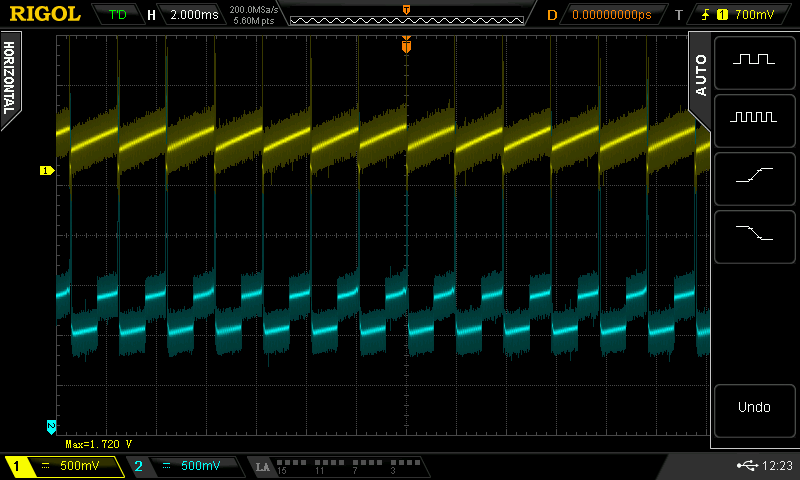

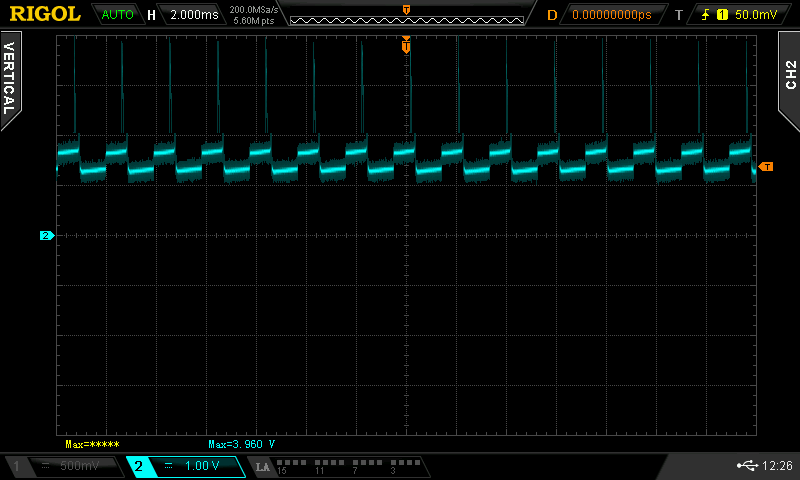

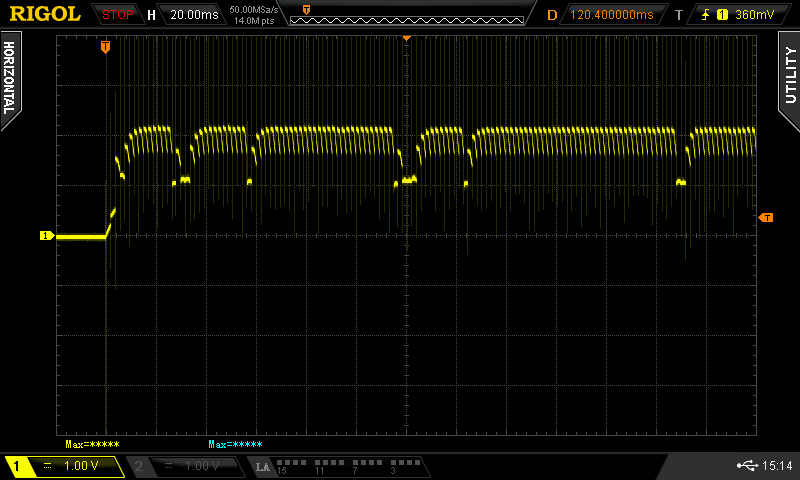

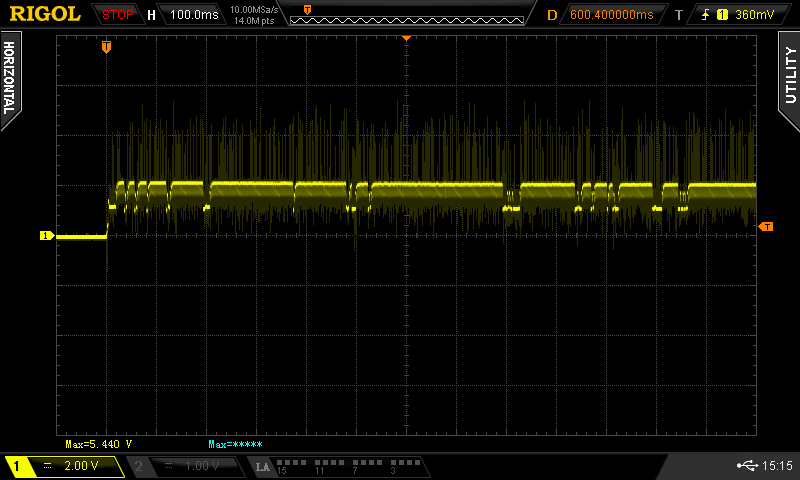

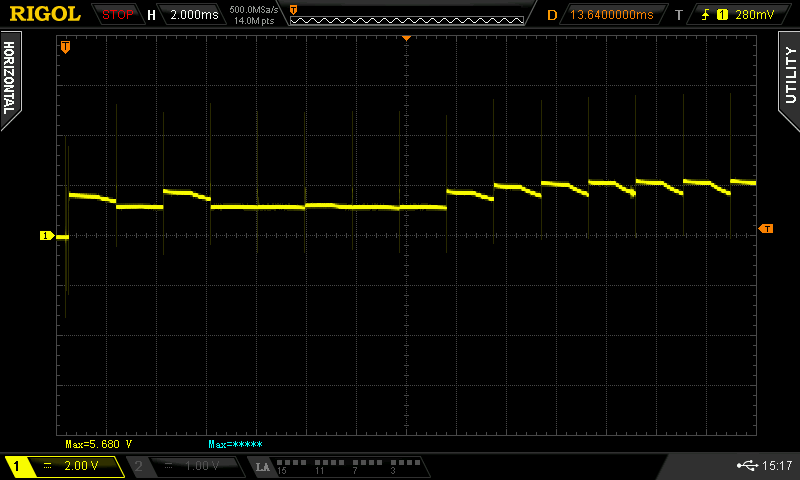

Now I have the bunch of PCBs manufactured and parts soldered on. The thing is that it is not working and I would like to get help solving this. On transistor gates there are no control vawe, just a small spike and then nothing. On Css (Webench) or C8 (Eagle) I have steady 5V, so I suppose some part of IC is working. What else should I measure to help determine where is the error ? Can upload the ocsilloscope view if needed.

Best regards

Dainius