Hi there,

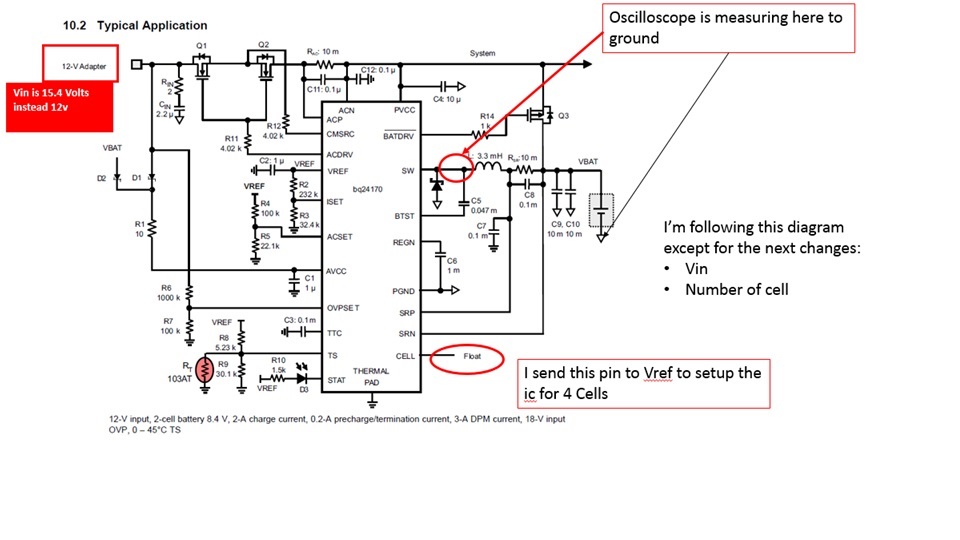

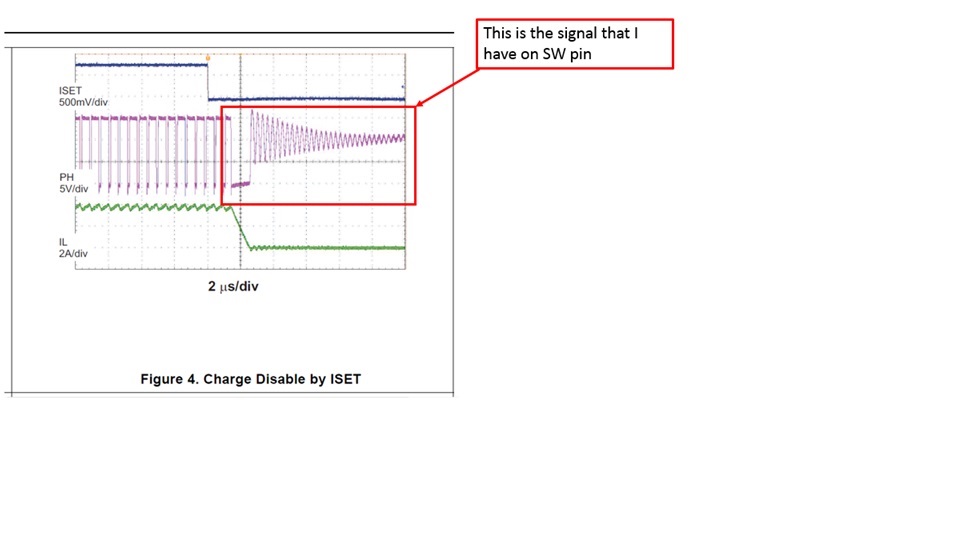

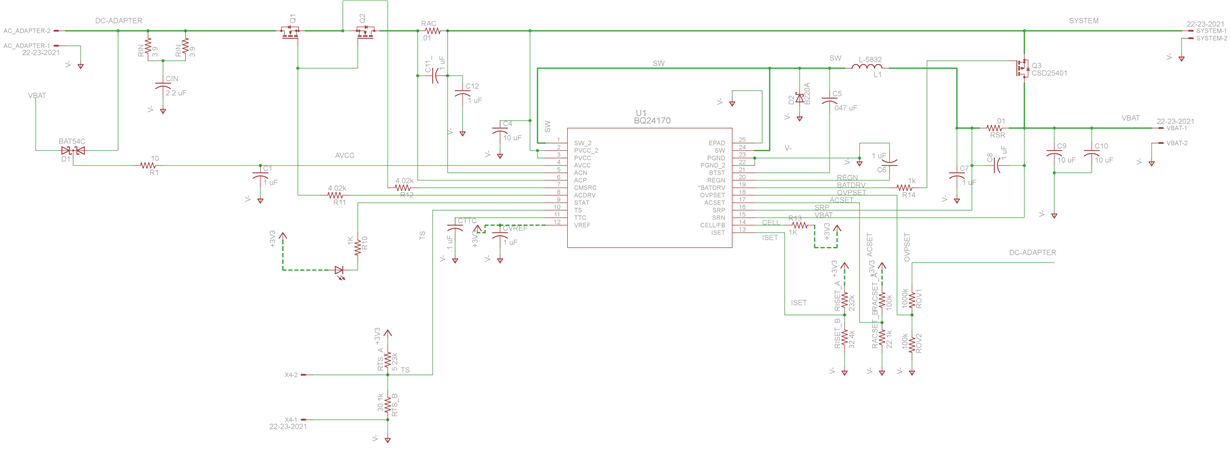

I'm triing to make a 3s2p li-ion charger, but it simple go to charge disable according to the figure4 on page 13 on the datasheet (slusad2c). i am conecting in this order:

1.-connect the battery

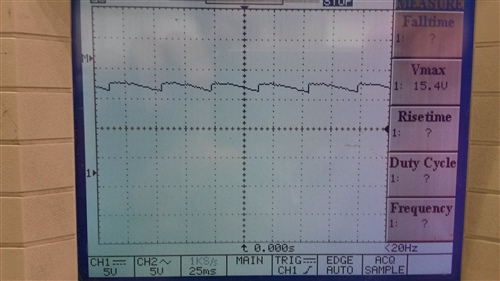

2.-conect the power supply(15.4 vdc),

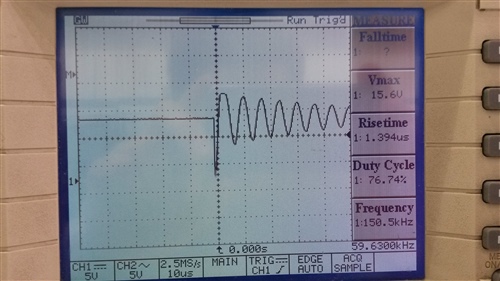

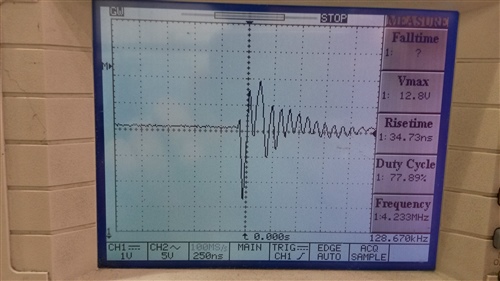

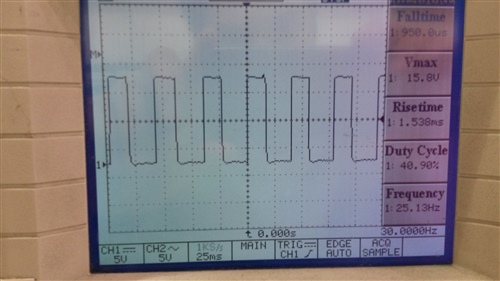

3.- aprox 2 second Vin is conected, status pin is low(this drives a led on), and at the same time i get the signal on SW, same as the figure 4 page 13 on datasheet (slusad2c)

additional information:

Vin=15.4V

nominal cell voltage= 3.7v

full charge cell voltage=4.2v

capacity per cell = 650mah

total capacity= 6*650mah= 3900mAh

Vbat=11.5 (voltage on a series of 3 cells,test of charging starts at this voltage)

Vref=3.298V

Viset= .400v(this sets fast charge at 2amp)

Vacset= .600v(this sets input current limit to 3amp)

Icharge= -.005amp

Vregn=6.00v

cell pin= 3.3v(conected to vref with 1kohm resistor)

power supply is able to source 3 amps.(tested directly to another battery without any charger)

pvcc= 15v