Other Parts Discussed in Thread: BQSTUDIO

Hello,

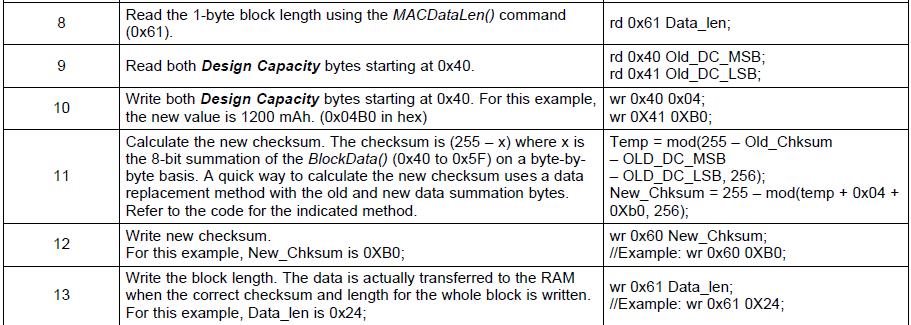

I am following the example in Chapter 6.1 in the SLUUBD4 BQ27220 user manual.

Steps 1 – 7 are working fine, but the data length in Step 8 (MACDataLen) returns 36. Since only 32 bytes (max) are possible for data transfer in the MACData buffer, how is 36 happening?

I have also tried setting MACDataLen to 32 before executing step 5, but 36 still gets returned.

The routine (attached) that I am having trouble with is BQ27220::get_data_32(....). Done on mbed.org K64F platform

uint32_t BQ27220::get_data_32(BQ27220_TypeDef& dataSTR, uint16_t sub_cmmd, int length)

{

if(length > 32) length = 32;

i2c_Buf[0] = BQ_SUB; //0x3e

i2c_Buf[2] = sub_cmmd >> 8;

i2c_Buf[1] = sub_cmmd & 255;

//pc.printf("dat-32a: %02x %02x %02x \r\n", i2c_Buf[0], i2c_Buf[1], i2c_Buf[2]);

_i2c.write((int)BQ27220_ADDR, i2c_Buf, 3, false);

wait_us(66);

Thread::wait(5);

i2c_Buf[0] = BQ_MACDATASUM; //0x60

_i2c.write((int)BQ27220_ADDR, i2c_Buf, 1, true);

_i2c.read((int)BQ27220_ADDR + 1, i2c_Buf, 1, false);

wait_us(66);

Thread::wait(5);

dataSTR.macSumReg = dataSTR.i2c_Bufx[0];

//pc.printf("dat-32c: %02x \r\n", i2c_Buf[0]);

i2c_Buf[0] = BQ_MACDATALEN; //0x61

_i2c.write((int)BQ27220_ADDR, i2c_Buf, 1, true);

_i2c.read((int)BQ27220_ADDR + 1, i2c_Buf, 1, false);

wait_us(66);

Thread::wait(5);

dataSTR.macLenReg = dataSTR.i2c_Bufx[0];

uint8_t lx = dataSTR.macLenReg;

//pc.printf("dat-32L: %02x \r\n", i2c_Buf[0]);

if(lx > length) lx = length;

i2c_Buf[0] = BQ_MACDATA; //0x40

_i2c.write((int)BQ27220_ADDR, i2c_Buf, 1, true);

_i2c.read((int)BQ27220_ADDR + 1, i2c_Buf, length, false);

wait_us(66);

Thread::wait(5);

for(int i = 0; i < length; i++) {

dataSTR.macData[i] = dataSTR.i2c_Bufx[i];

pc.printf("%02x ", dataSTR.i2c_Bufx[i]);

}

dataSTR.checksum = calc_checksum(dataSTR, lx);

pc.printf(" mdl: %3d mdcs: %02x cs: %02x \r\n", dataSTR.macLenReg, dataSTR.macSumReg, dataSTR.checksum);

return ((uint32_t)dataSTR.subReg);

}