Other Parts Discussed in Thread: TPS65130

Hello,

I am currently trying to TPS65131 for an audio project. My requirements are:

* single LiPo Cell source

* +/- 12V output

* up to 100mA per side

* no noise in the audio band

For Reference, my scematic and Layout:

(please note: the 100u tantal caps are not present at the moment. The 10u caps are 22u ceramic types at the moment)

The following is true:

* +12V works as desired in all below described screnarios

* with no load and power-safe on, -12V ramps up and stays relatively steady at -12V

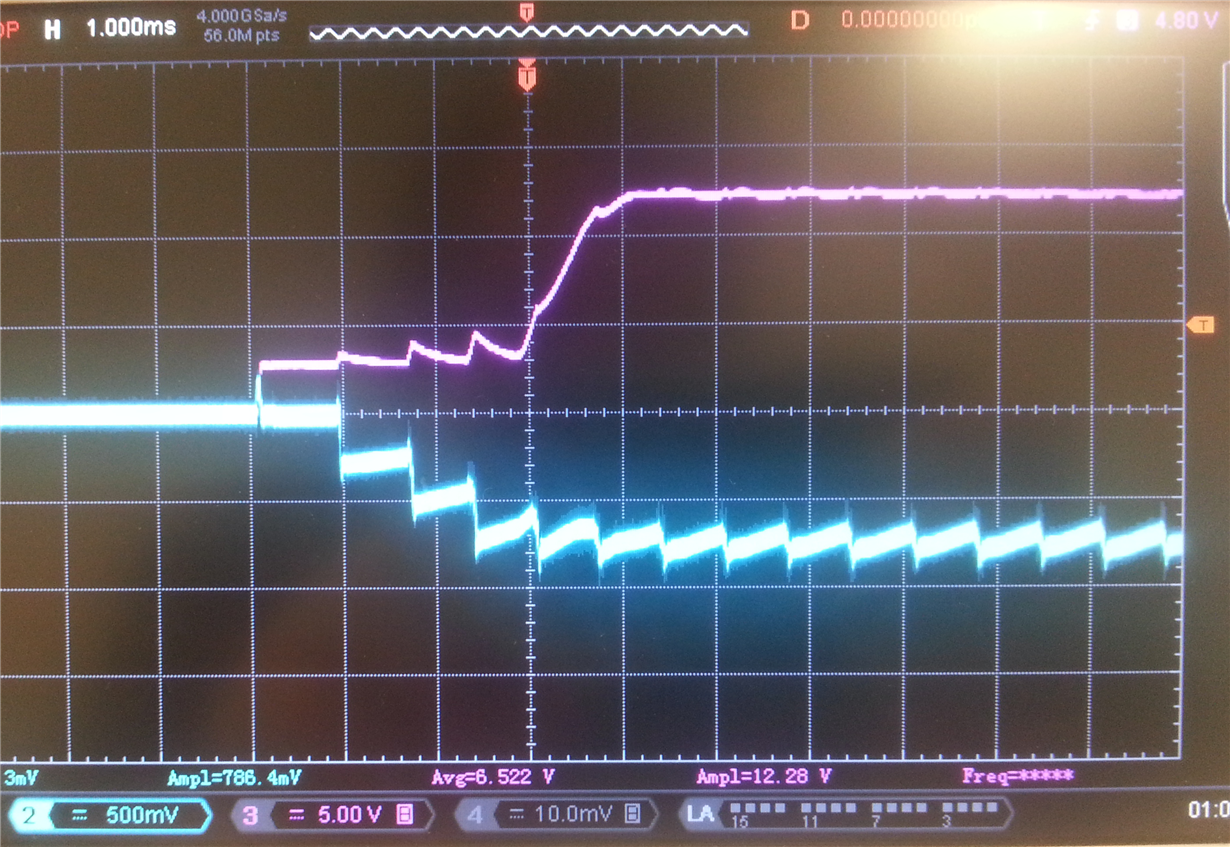

* with no load and power-safe off, -12V ramps up, but produces large 5V jumps in a sawetooth-manner

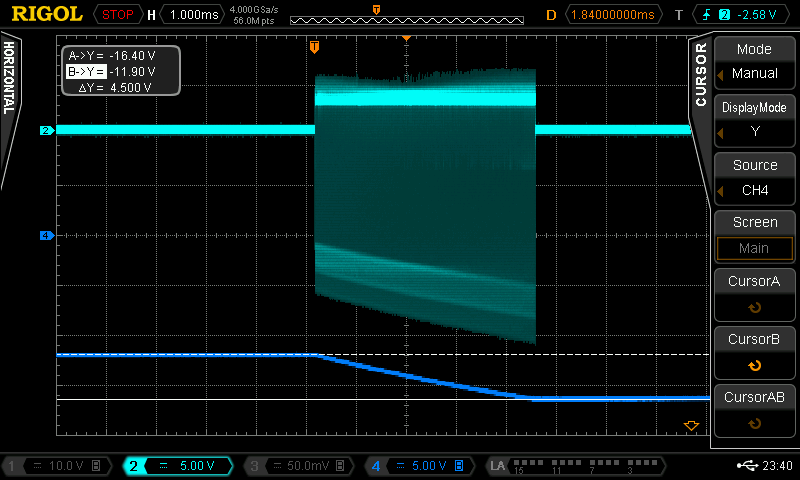

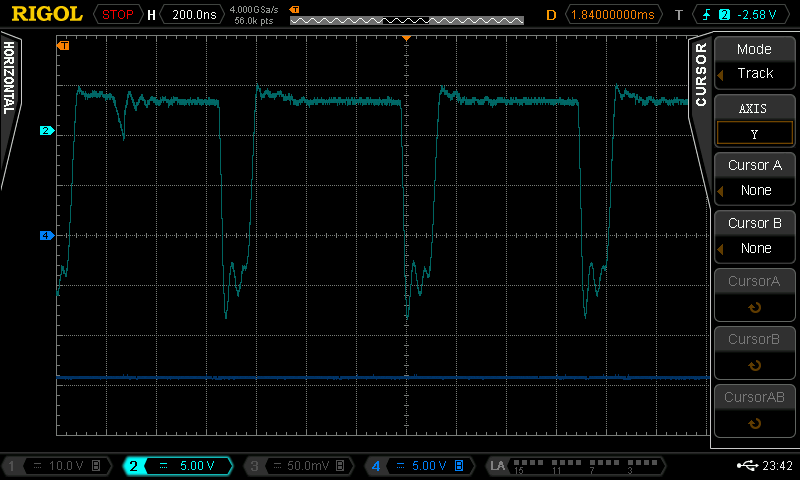

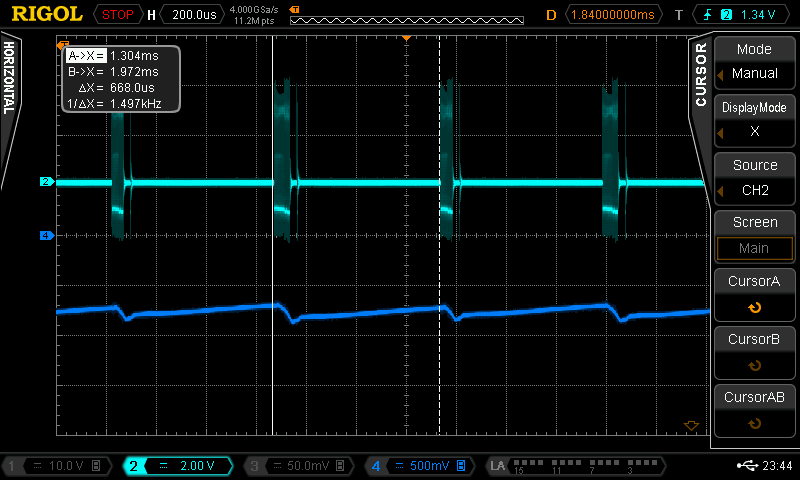

* with about 50mA Load and power-safe on, -12V fails to ramp up (sticks at ~ -0.2..-0.3V) and ~1..2 kHz noise is audible

* with about 50mA Load and power-safe on, -12V fails to ramp uo and ~1..2 kHz noise is audible

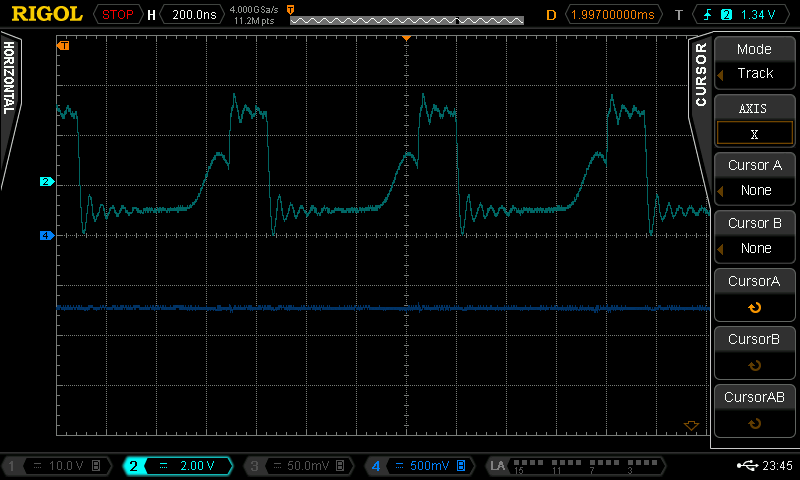

Here a Scope-Shot from one failed ramp-up attempt. The blue curve is the failed attempt.

Measured under load Condition:

FBN: 1.064V (injected noise present)

VREF: 1.215 (injected noise present)

OUTN: -750mV (sawtooth, as shown above)

Ground potential is virtually the same on the board (in the range of 1..2 mV) and does however exhibit injected noise (then again, only a couple of 10mV)

The following threads have already been consulted:

https://e2e.ti.com/support/power_management/non-isolated_dcdc/f/196/t/626451

https://e2e.ti.com/support/power_management/non-isolated_dcdc/f/196/t/607104

https://e2e.ti.com/support/power_management/non-isolated_dcdc/f/196/t/617831

https://e2e.ti.com/support/power_management/non-isolated_dcdc/f/196/t/585589

The following was tried:

* removing C15 (still does not ramp up)

* increasing C15 to 20p (still does not ramp up)

* using 6.8p and 100k in series instead of C15 alone (decreases no-load fluctuation amplitude significantly, but still no ramp-up)

The question is:

Why does the negative converter does not ramp up under load? Wham am i missing here?

Thank you a lot for help !

Kind regards