Other Parts Discussed in Thread: UCC28063, LM5112

Hello all,

What are some things to look for, to improve the phase relationship between Phase A and Phase B?

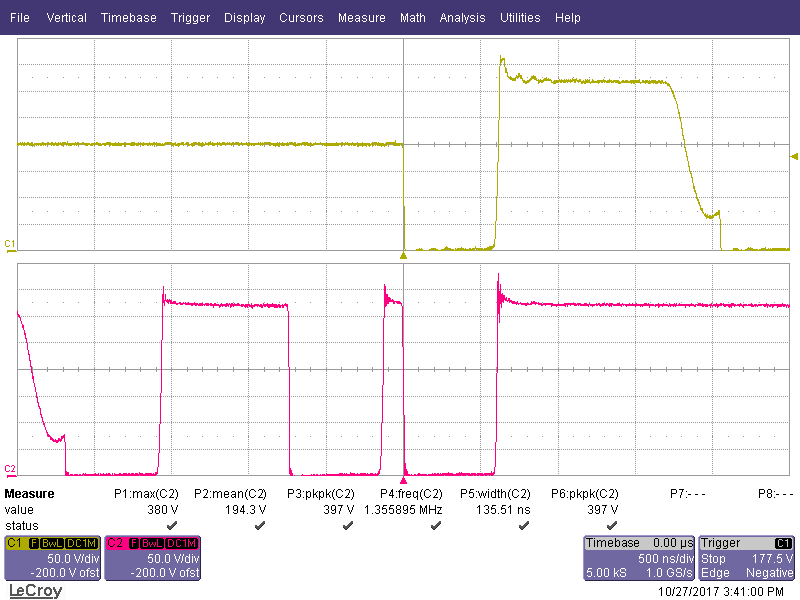

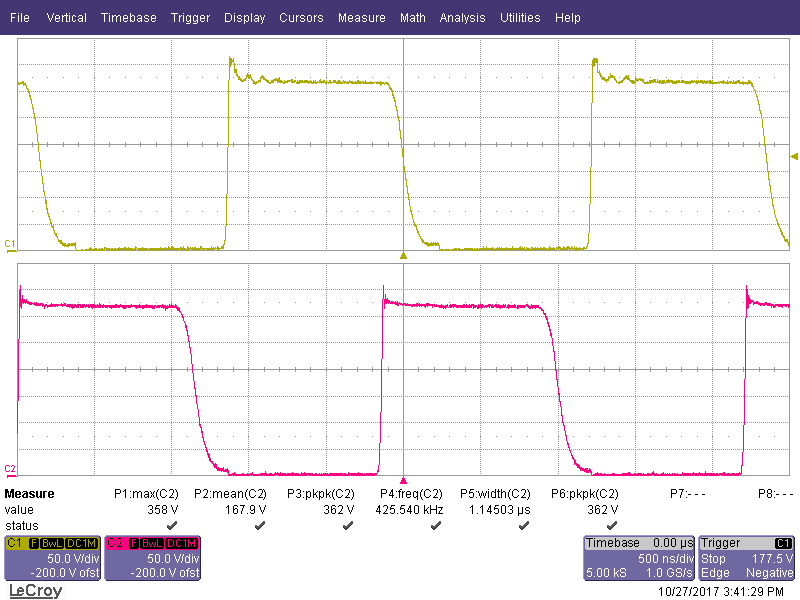

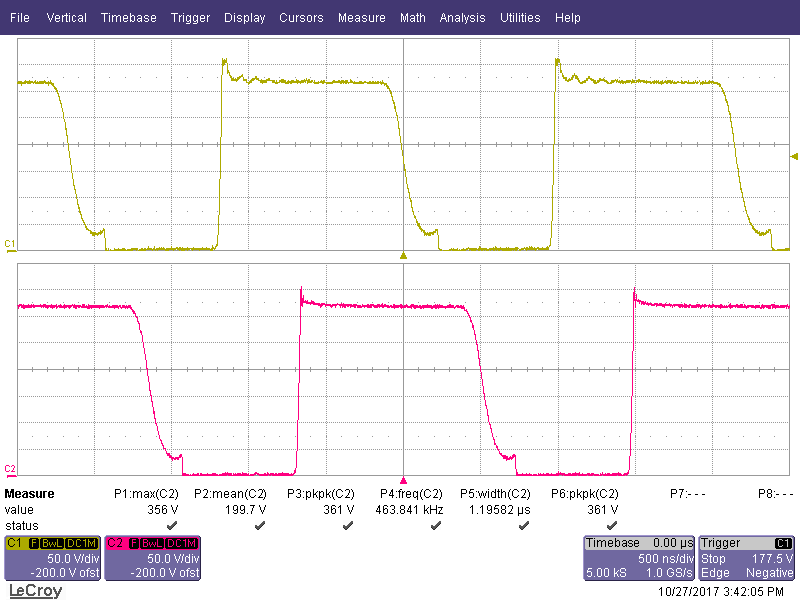

Right now I'm getting about a 100 ns error. The on-times are identical, and ditto the signals on ZCDA and ZCDB.

TIA