Hi,

We got a question from the customer about LM5140-Q1.

Could you help us?

[Question]

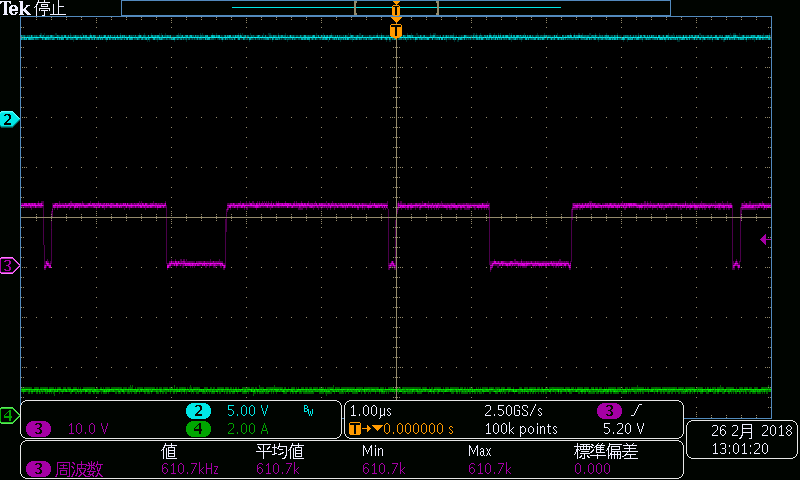

They are evaluating LM5140EVM and found big switch node jitter. Please refer to attached file.

LM5140Q1 test result_Feb2618.pptx

- Case 1 -

Condition: EVM default setting(2.2MHz operation)

Phenomenon: The switch node jitter of Vout2(5Vout) is bigger than Vout1(3.3Vout).

- Case 2 -

Condition: 440kHz operation; they changed the value of external components. please refer to attached file

Phenomenon: The switch node jitter of Vout2(8Vout) is bigger than Vout1(3.3Vout).

They assume the jitter becomes big as output voltage setting is rised. They have questions about this phenomenon.

- Why does the jitter become big as output voltage setting is rised?

- Are there any solutions for this phenomenon?

Best Regards,

tateo