Other Parts Discussed in Thread: TIDA-00120, TIDA-00121,

We followed the PMP7605 reference design in creating our own MPPT controller. (We used an STM32F410 CPU in place of the MSP430 however)

As I have never worked with this type of circuit at this low level, I need to get some additional information about what I am seeing in terms of it's operation before I proceed with connecting a lead acid battery to V_OUT and a solar array (or a current limited power supply) to V_IN.

As of now, I have only connected a 12v supply to V_OUT in order to power up the board and perform functional testing of the processor and to look at how I am switching the gates of the MOSFETS. One of my observations is that voltage appears at V_IN to GND which is roughly 2x V_OUT i.e.12v at V_OUT gives me 24v at V_IN. Is this normal behavior for this circuit? (I am aware that I will need a blocking diode to prevent the battery from driving the solar array) Aside from any leakage through the upper MOSFETS, should I expect to see voltage at V_IN? If so, what should I expect that voltage to be? Another observation is that when I am not driving the MOSFETS, I have my supply voltage at on V_OUT appearing at V_IN and am assuming that this is due to the body diodes conduction in the upper MOSFETS.

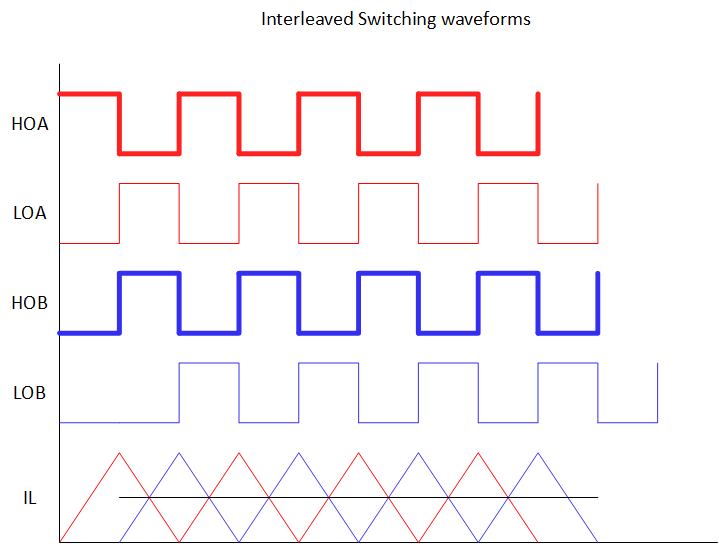

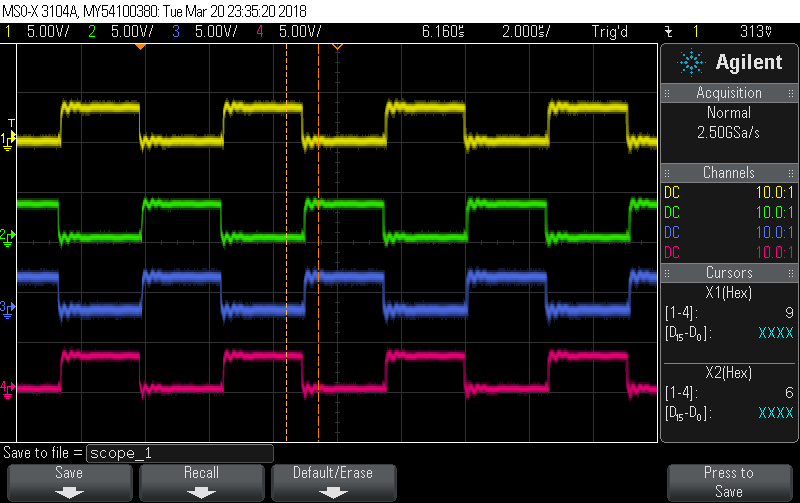

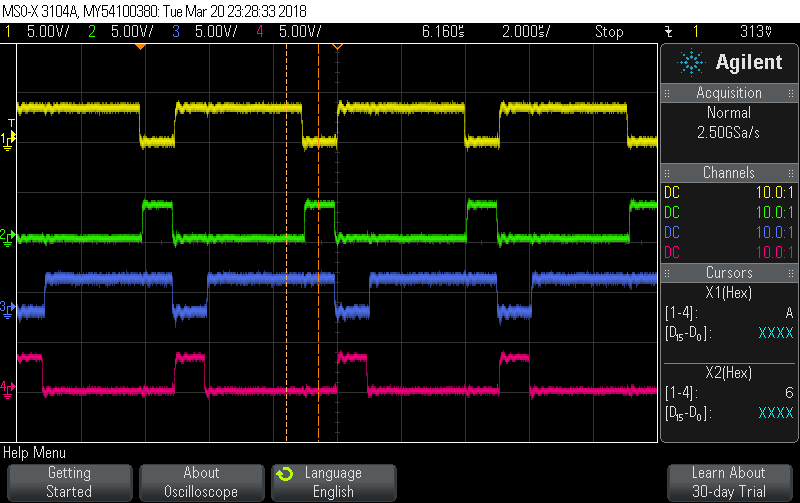

I would also like to get some clarification on how to drive the MOSFETS in the bridge circuit, Currently, I alternately drive HOA / HOB on, LOA /LOB off and then HOA / HOB off, LOA /LOB on. Is this the correct way to drive the bridge or should I only be switching one side at a time as opposed to both in parallel?