Other Parts Discussed in Thread: TIDA-00778, TIDA-00909, TM4C1294KCPDT, UCC27712, , UCC21220, LM5170-Q1, DRV8301

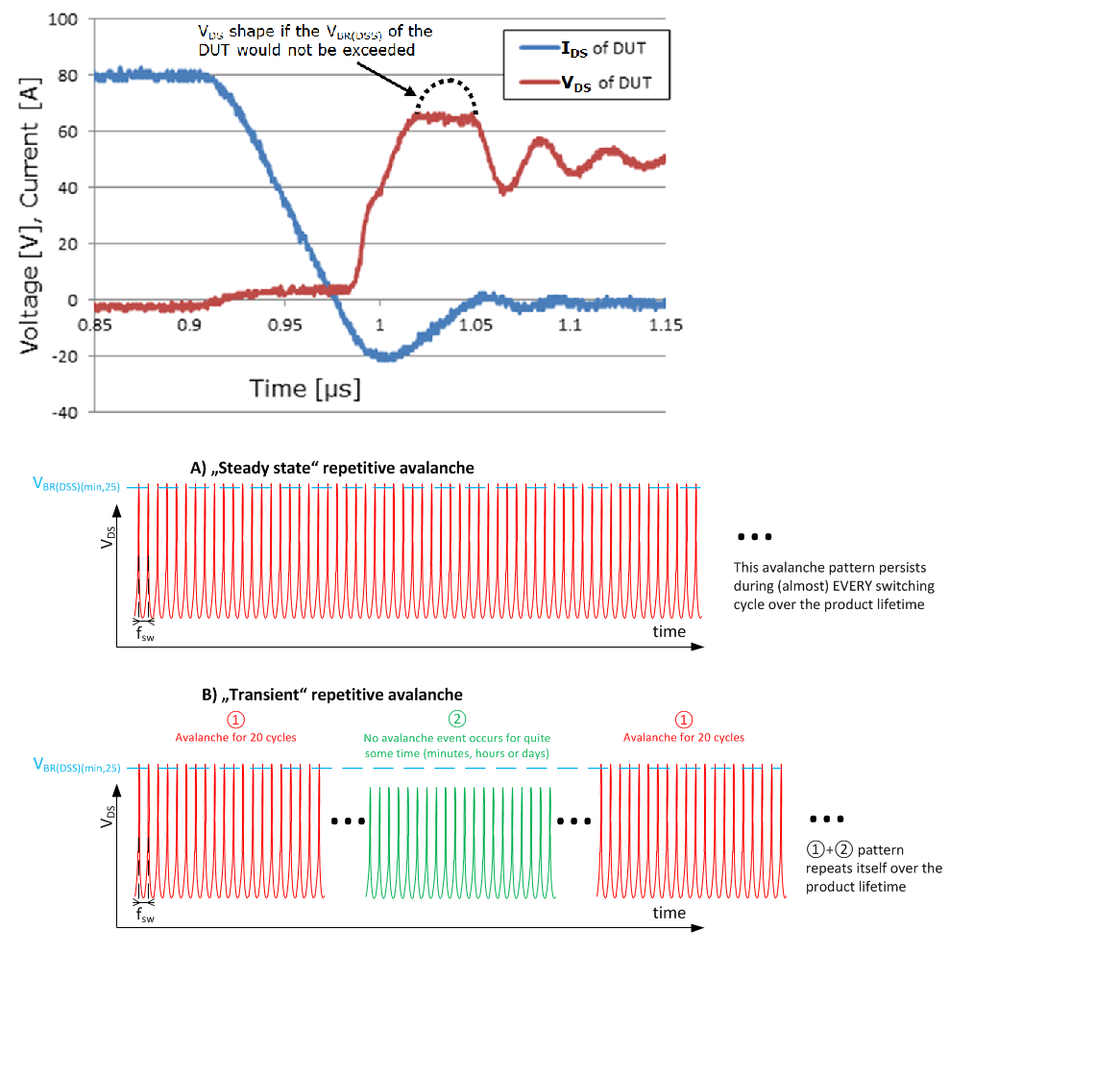

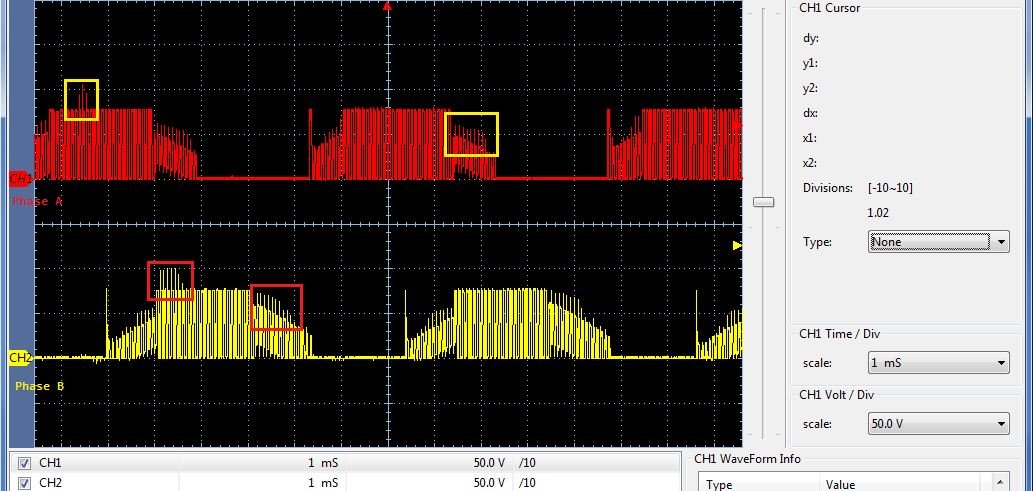

What can be done to calm 10Mhz ringing of HO output causing random very high VDS peaks? Is there some way to reduce HO output bias slowing the rise time other than adding excessive amounts of gate drive resistance or adding gate capacitance? It seems the flat top is more indicating of IAS events than we currently are seeing.

Adding gate capacitance seems counter intuitive to what TI documents are claiming about LS/LD/Q. Can the typical HO gate drive pull down resistor value connected to HS effect the HO output signal if it is to large in value? Why is there no mention of TI gate drivers HO output causing turn on oscillations when NFETS are being used versus IGBT modules? The problem is the source side voltage peak shown in captures can exceed VBR(DSS) at higher working voltages if left unchecked.

These voltage spikes seem much worse with the faster UCC and how much gate resistance is considered to much for small QG-NC values? Can COM pin tied to ground plane lead to high VDS spikes when digital ground is isolated from analog ground or COM? Note the HO output capture above is not consider avalanche being the top is not flat as shown below but it easily could enter IAS with higher working voltages exceeding VBR(DSS).