Other Parts Discussed in Thread: PMP20001, UCC21520,

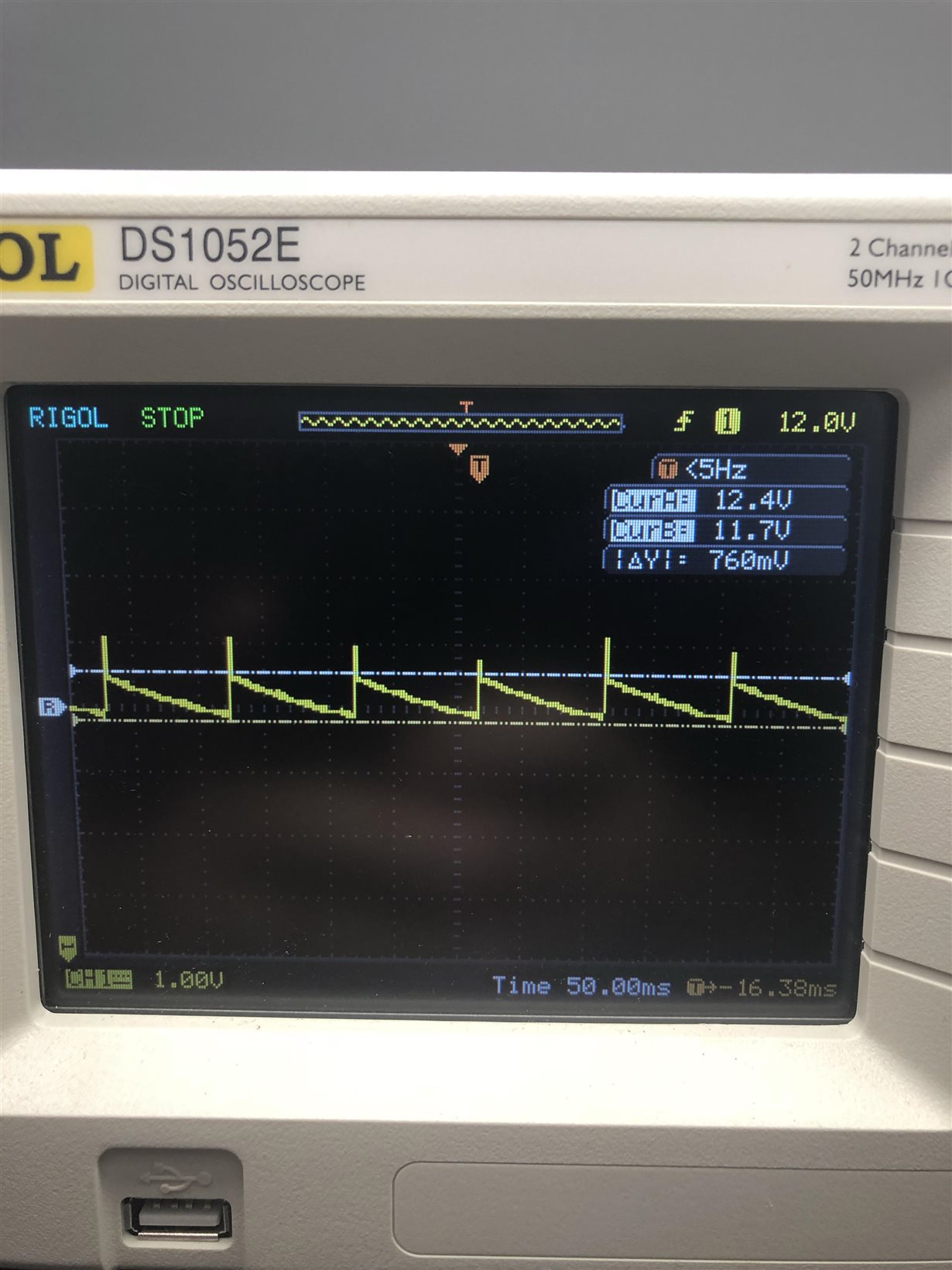

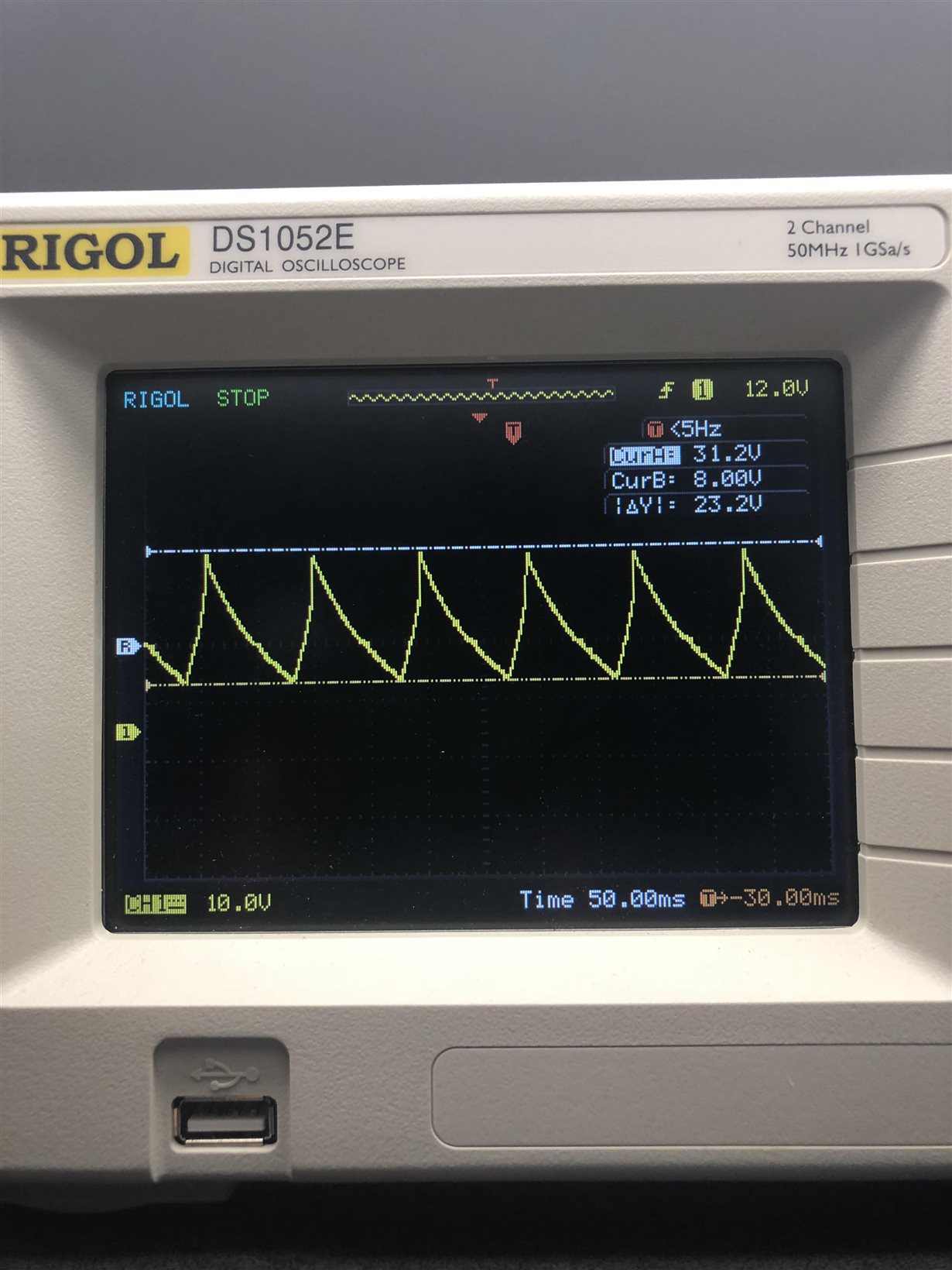

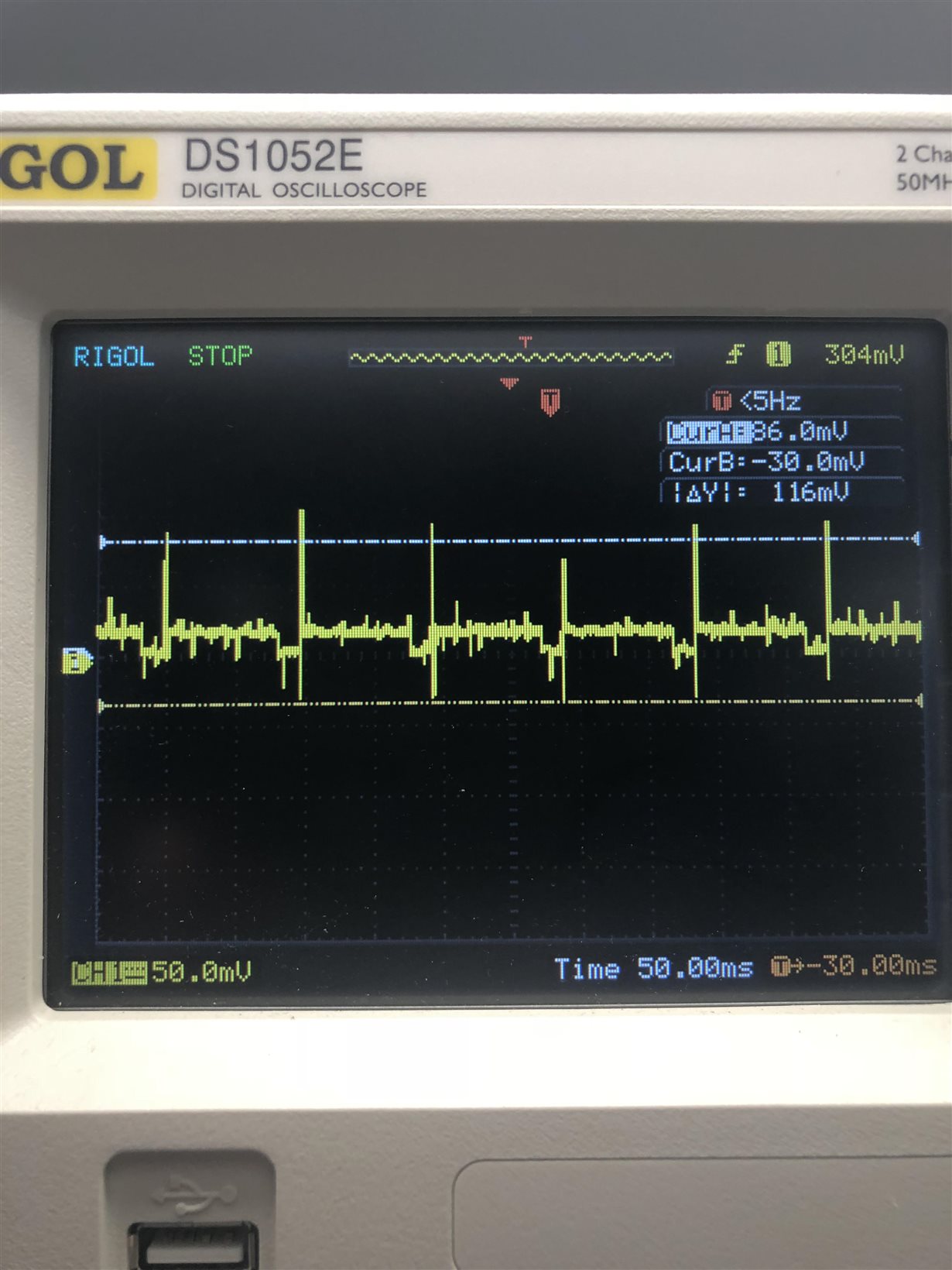

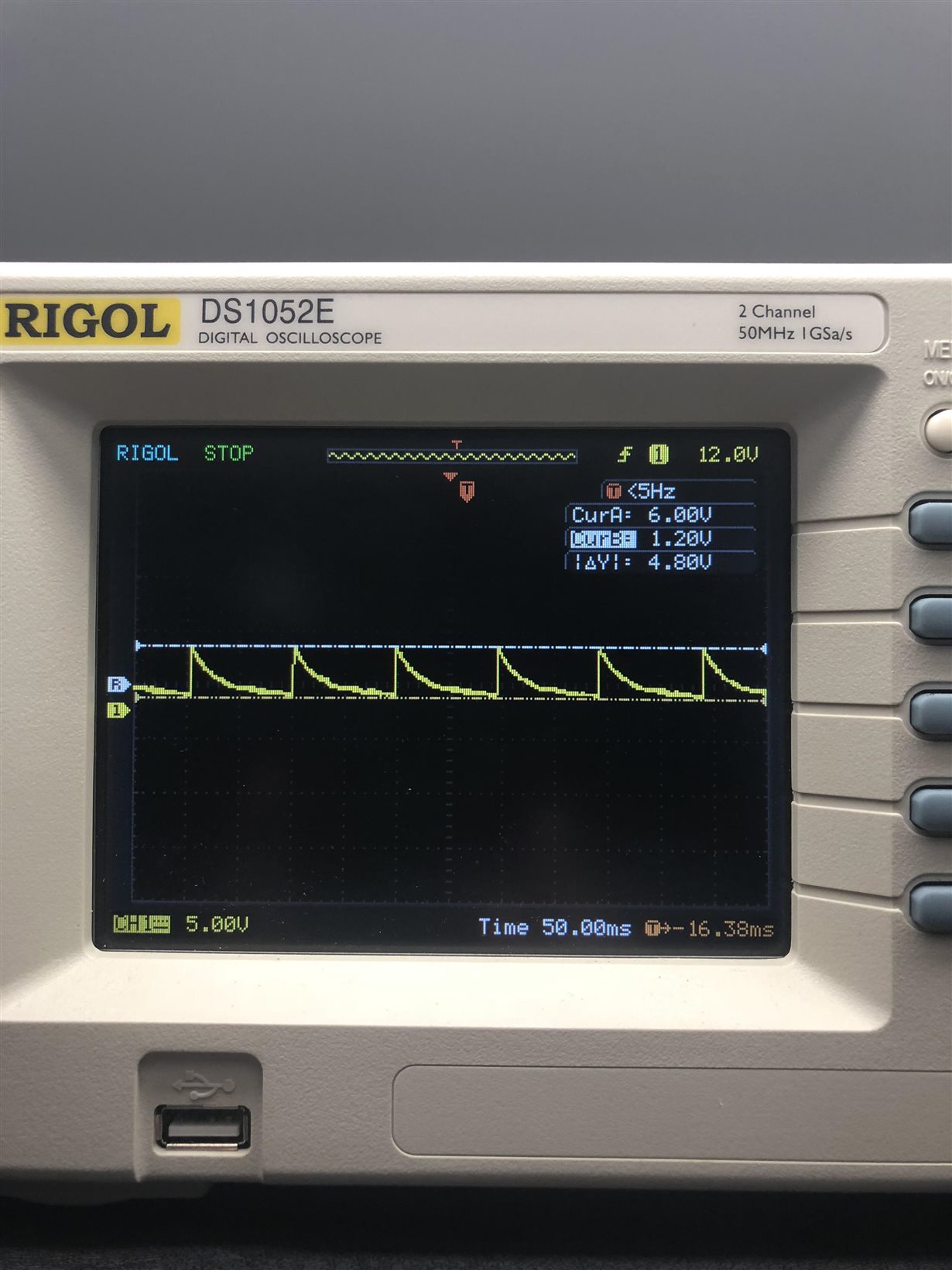

Was hoping someone could take a look at our schematic and see if there is anything obvious. R68 has already been changed to 5 ohms (stacked 2 10 ohm resistors). And node between D2 and C86 should also be connected to VDD. Even with these changes I am not getting a good 20V on VDD and am wondering if that is the cause. The other major difference is the fet in PMP20001 was listed as NRND so we substituted for a better one, does the Rds-on change the value of R70?

Thanks for any help.