Other Parts Discussed in Thread: TIDA-00778,

Hello,

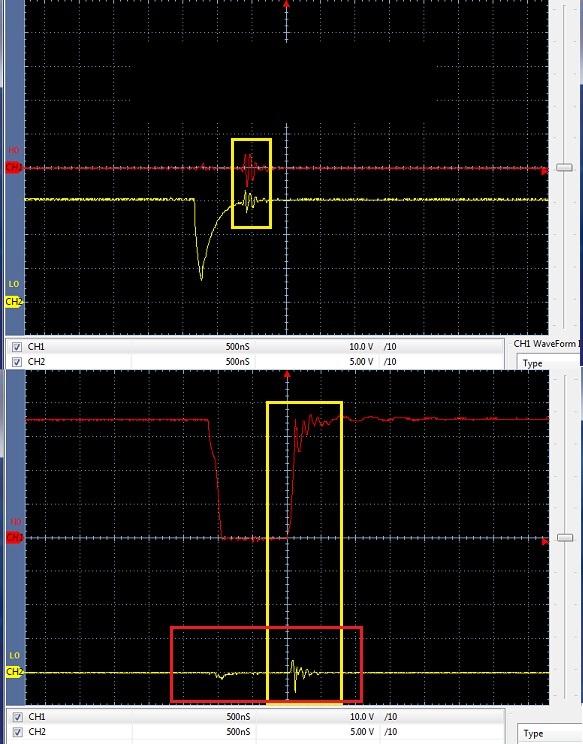

Please help determine why synchronous dead band delay (80ns) HO falling, LO rising edges seem to cause LO ringing along ground (-5-10v) during HO fall/rise pulses. When dead band immediate update, LO falling/rising edges cause HO ring residue pulses during LO low pulse times. Overlapping PWM signals on HI/LI inputs drive the HO/LO outputs produce dead band delay only for last PWM cycles Ton NFETS. The last on NFETS exist across two of three UCC, one high side one low side.

Perhaps internal creepage or indirectly HI/LI cause dead band delay residue on opposite outputs? Could HI/LI input filter (200pf/51ohm) be causing cross talk on AGND that LO picks up via COM?

How can HO/LO dead band residue ringing pulses be mitigated?