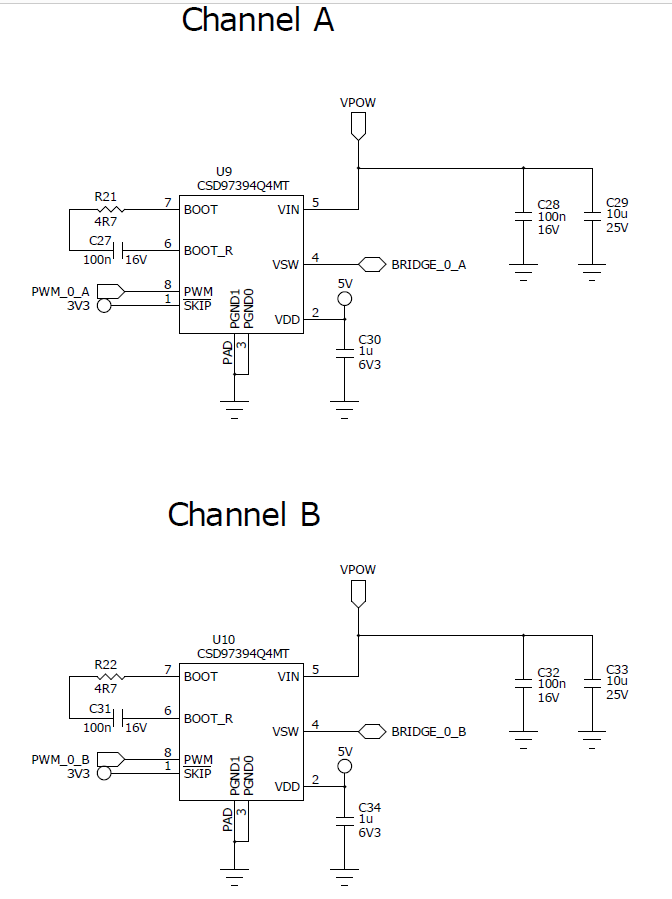

In our implementation for the CSD97394Q4MT as BLDC driver we are observing that the channel with lower PWM duty cycle is not able to pull the voltage low. Please see schematic below:

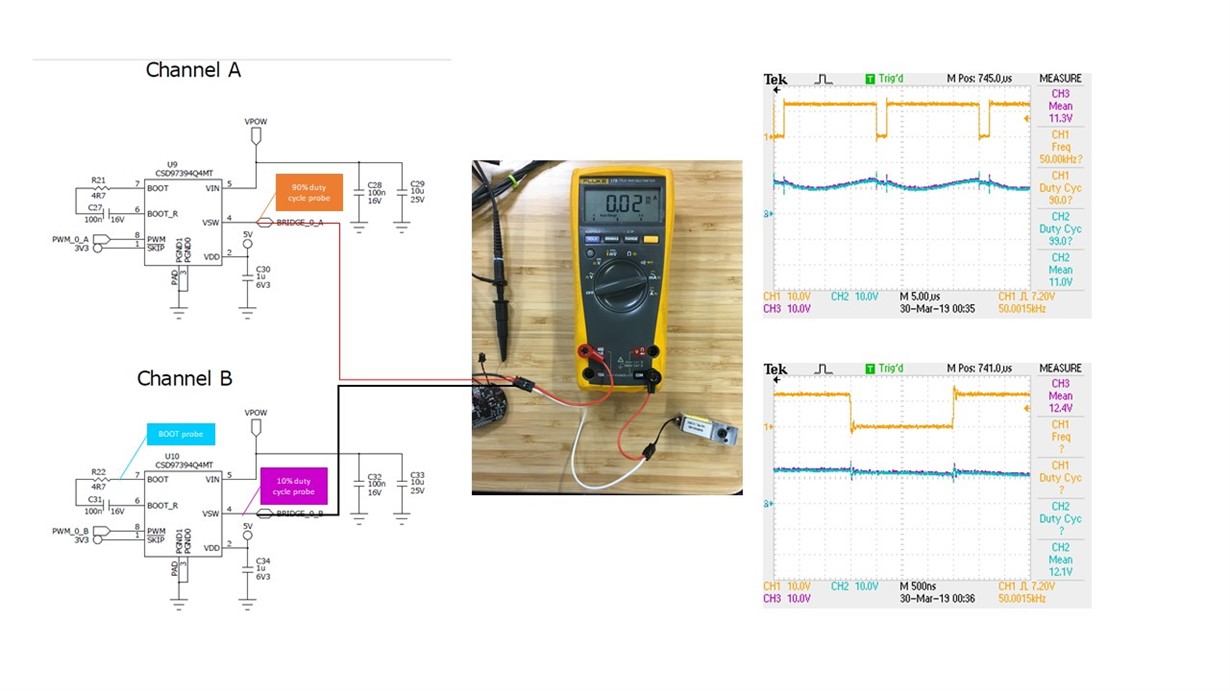

We are connecting one lead of a solenoid to BRIDGE_0_A and the other lead to BRIDGE_0_B, the solenoid is rated for 12V (68 Ohm resistance). We are injecting two PWM (50 Khz)) signals to Pin 8 on each channel. The duty cycle for CHANNEL A is 90% and 10% for CHANNEL B, image bellow shows the output in VSW pin (BRIDGE_0_A and BRIDGE_0_B). Orange and Cyan signals are what we measure from the VSW pins (BRIDGE_0_A and BRIDGE_0_B) when the bridge signal is not connected to the solenoid, and the Green and Purple signals are the output we are measuring (with oscilloscope) when the solenoid leads are connected to BRIDGE_0_A and BRIDGE_0_B (VSW pins for each CHANNEL). For some reason the channel with lower duty cycle is not able to pull the signal low sometimes, and we will observe the same result if we invert the duty cycle for the channels.

Any idea of what could be happening is appreciated.

Thank you for your time.