Other Parts Discussed in Thread: TPS62133, ,

Hi,

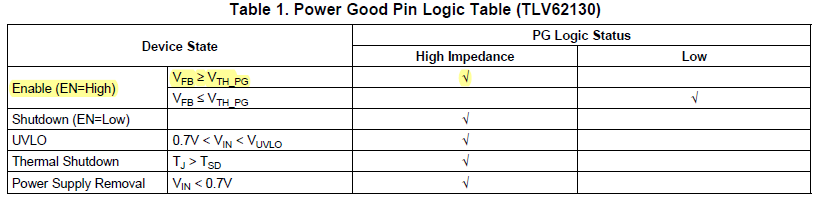

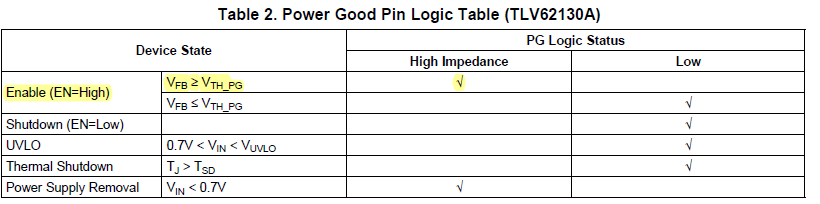

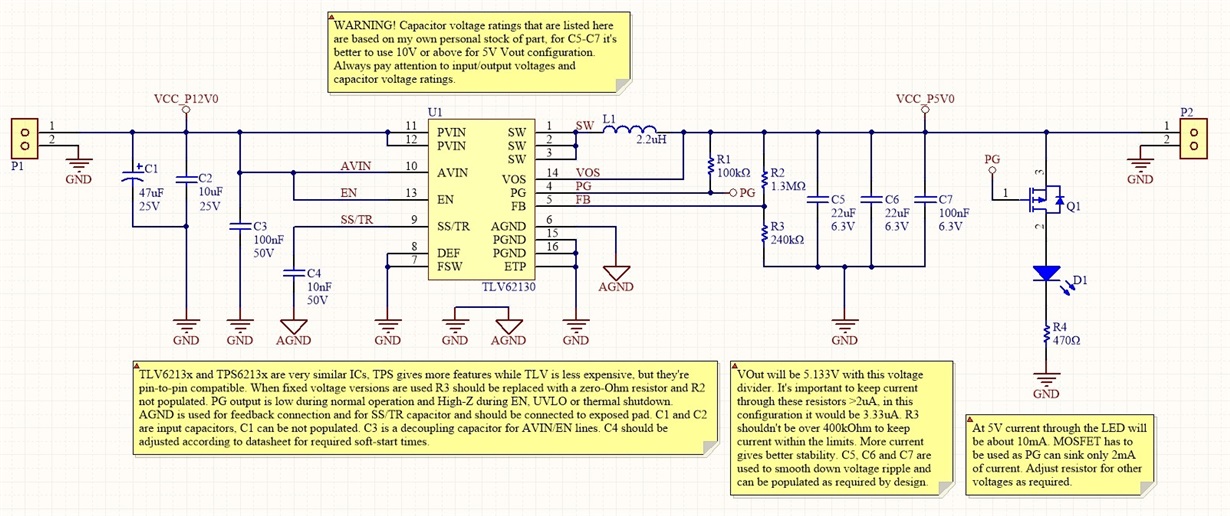

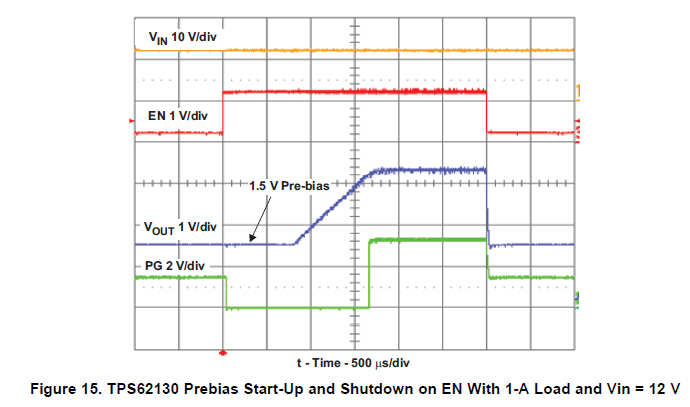

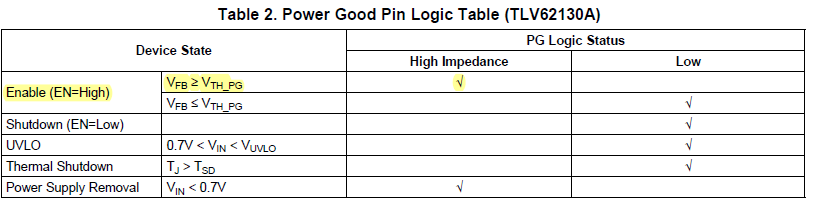

I'm experiencing a problem with PG pin of the TLV62130. As per manual: 'With TLV62130 it is high impedance when the device is turned off due to EN, UVLO or thermal shutdown.' In my design it's pulled up via 100kOhm resistor to the output of TLV62130 but in my case PG is always staying high, even when IC is working normally and not shut down by EN pin or under UVLO/thermal shutdown. TPS62133, when put onto the same board, controls PG pin without any issues, it's pulling it low during normal operation. My design is just a generic one based on TLV6213x EVM module and part's datasheet. Thanks!