Hi John,

1,

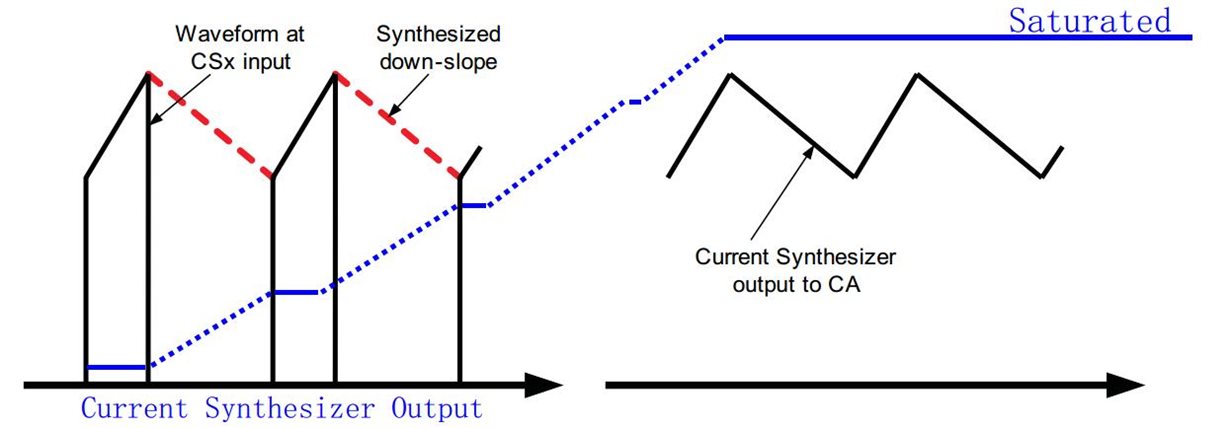

So,during inrush surge events at power up and AC drop-out recovery, VVSENSE < VVINAC, the synthesized downslope becomes zero like the blue curve I drawn below?

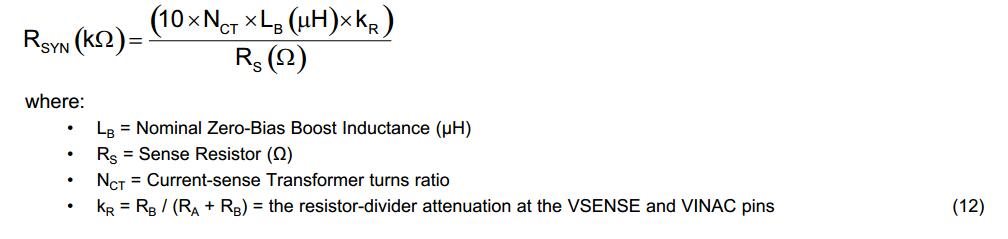

2, During normal operation, off-time down-slope emulation is decided by the formula below.

But, how could you ensure that the down-slope emulation is accurate while the L value would change with the current flowing through it??? I mean, L changes, down-slope changes, but the formula above didn't take the inductance variation into consideration.