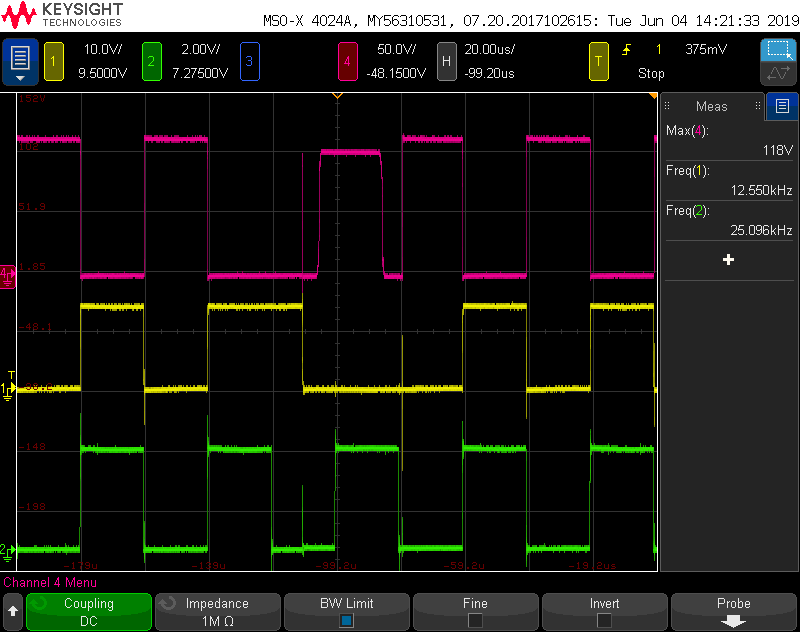

I am using two drivers to control either side of an H-bridge. One if these drivers has an issue where the outputs occasionally latch and hold their state such that they do not match their corresponding HI/LI input. [See attached image: Green - LI, Yellow - LO, Pink - HO.]

The main recurring issue is when the LI input transitions to low but the LO output remains high. The HI input is the inverse of LI and also does not change at this point. Some amount of time after the input change (>1us), the output changes but then misses the next edge and so on. This continues for several cycles before the driver catches up again.

The PWM drive signal is running at 25-26kHz with 50ns deadtime between LI and HI inputs. I have tried: replacing all hardware, adding capacitors to the LI/HI inputs, increasing the capacitance of the supply capacitor.

From the datasheet I cannot see any situation whereby the LO output would be high whilst the LI input is low. Can anyone explain why this may occur?

The supply rail does not drop out, nor is there any issue with the inputs to the driver.

See schematic below: