Other Parts Discussed in Thread: LM5176, INA181

Hi

I have the same problem as here : https://e2e.ti.com/support/power-management/f/196/t/648997?LM5175-LM5175-Synchro-Management-of-Boost-Highside

My project : Input 12-15 V (battery); output 13.8/14.7 V into antoher battery ; 30 A max. (battery charger). IC : LM5175.

The problem is that high transistor of the boost side of the bridge it is not switched by the driver. It can not work as a diode , given the output current needed. So the diode emulation feature is a must. But it seems to not working as expected.

In DCM mode the high transistor of the boost side of the bridge is driven only in specific conditions, namely :

- when the converter works in buck mode : the gate is driven

- when the converter works in buck-boost mode : the gate is driven only on half the switching period

- when in boost mode: the gate it is not driven at all (works as diode )

Can the problem be because the IC does not sense when the current through inductor falls to zero ? Also regarding this, how does the IC senses the current through inductor in DCM mode?

How does the IC senses the current through inductor in boost mode ? Because in boost mode there is no current at the common source shunt.

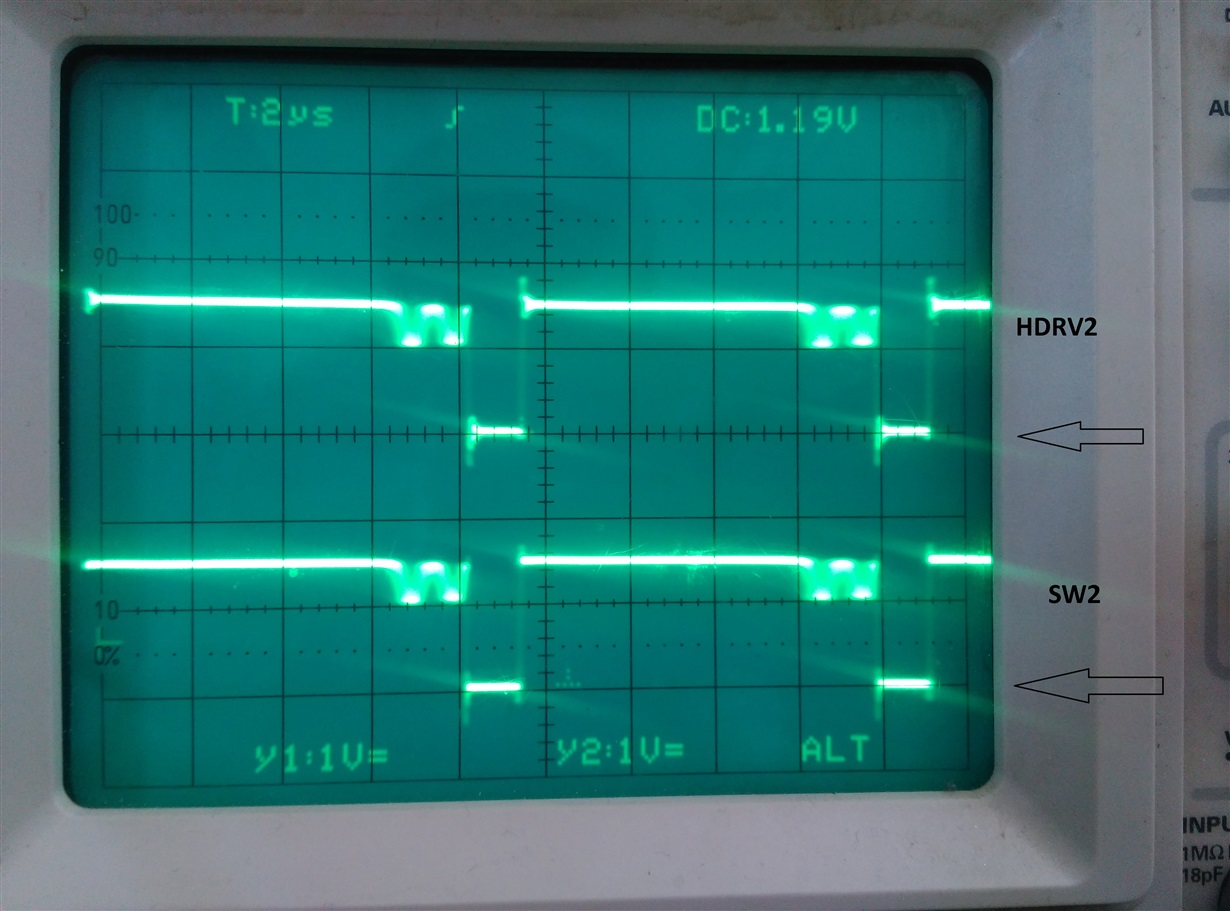

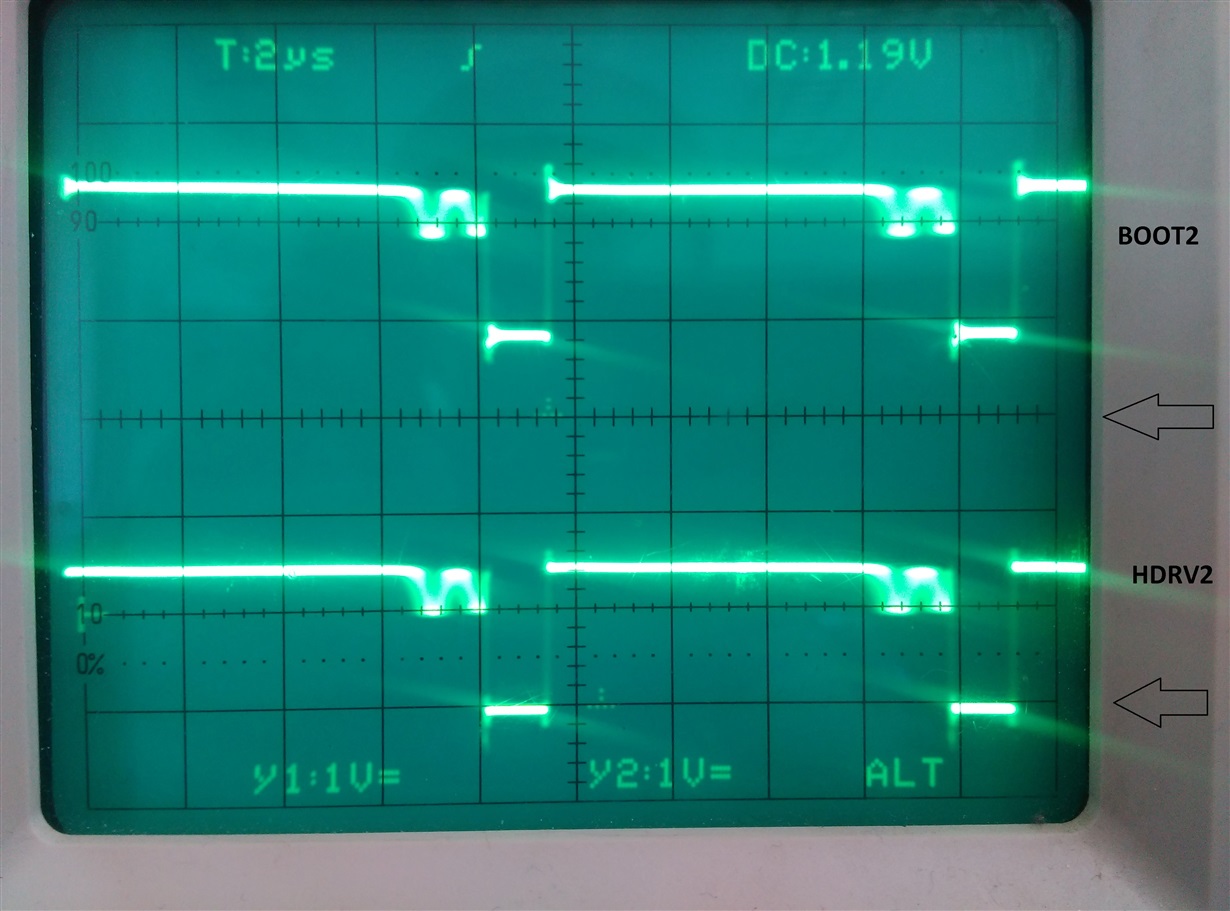

See photo (waveform : HDRV2 referenced to PGND)