Hi,

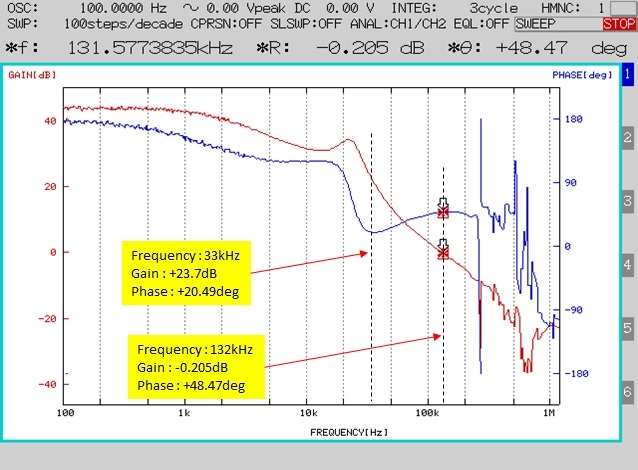

The attached image is the bode plot obtained using TPS62136EVM-698.

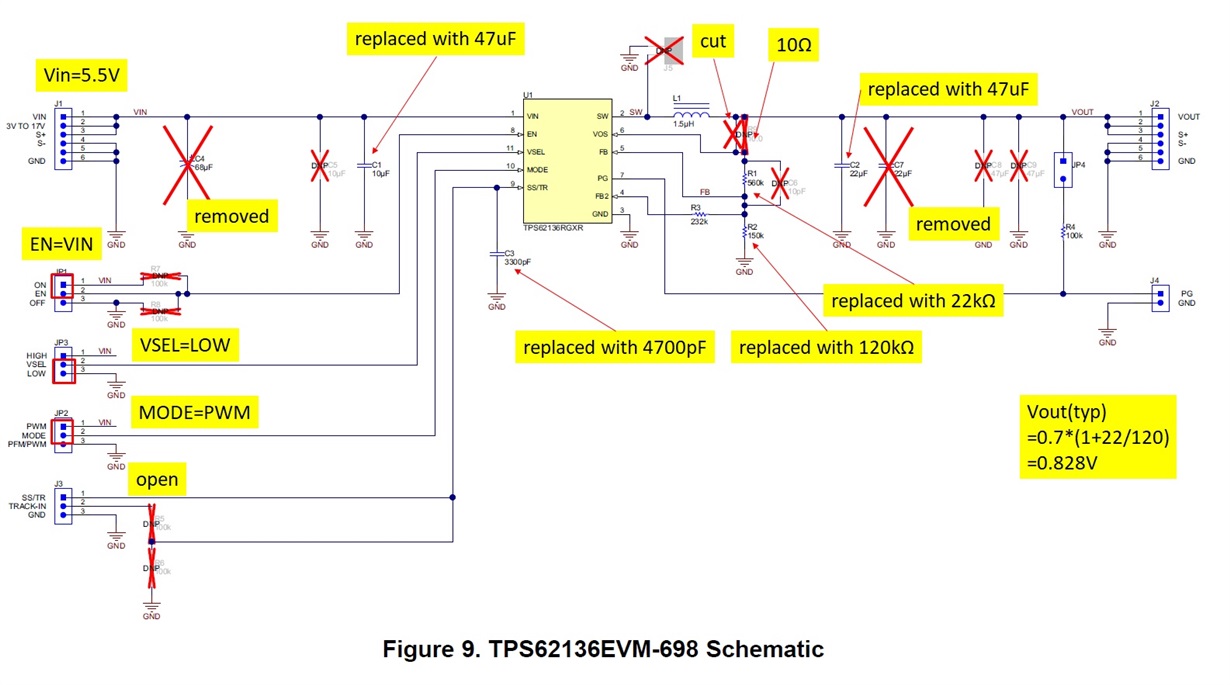

The schematic is also attached.

Is this circuit stable and has small over/undershoot at load fluctuation?

If not, please tell me how to improve stability.

The phase at 0dB is about 48deg, and the phase at this point (=phase margin) is considered to be sufficiently large.

However, I think it may be unstable because the phase is as small as about 20deg at around 30kHz.

I have confirmed that the phase margin improves by reducing the value of the output capacitor,

but the output voltage ripple increases and does not meet my requirements (less than 20mVpp at 5.5V-9.5V).

Also, adding Cff seemed to have little impact.

Thanks