Other Parts Discussed in Thread: AM3356, , TPS65218

Dear experts,

We use this PMIC to power AM3356. Two years ago, we reported the same start-up issue in our module with -B0 sillicon revision on DCDC4. Your team recommended us to change PMIC to a new sillicon revision -D0. All affected boards were fixed with 330pF workaround in L4 coil and this problem seemed to be fixed. Currently, we have experienced DCDC4 start-up issues again reported by the client. Reading a lot of posts in this forum, I try to collect all test I think you need.

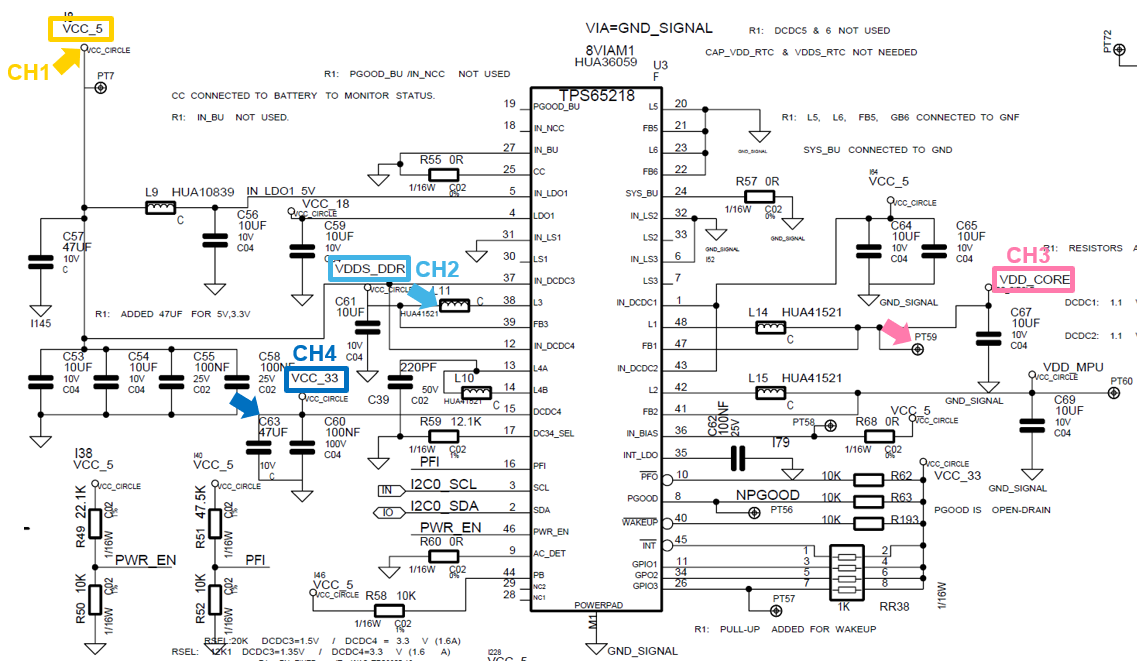

Firstly, PMIC schematic with oscilloscope channel marked for your easy identification.

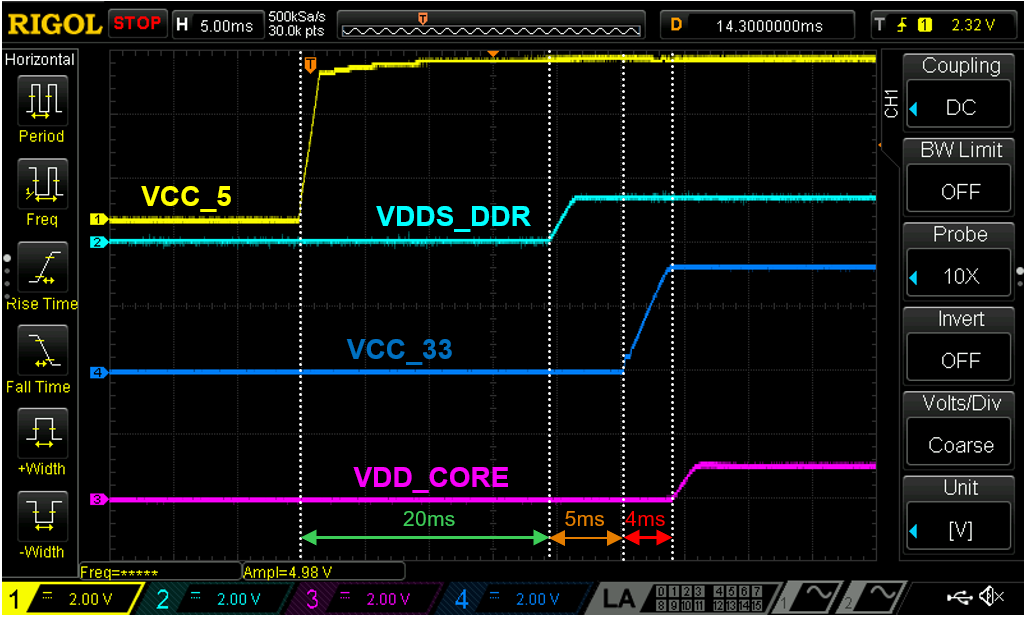

Second, you can see the ocilloscope captures in two cases: Start-up sequence correctly and Start-up sequence failure. These captures were taken in the same module and its performance is fully random.

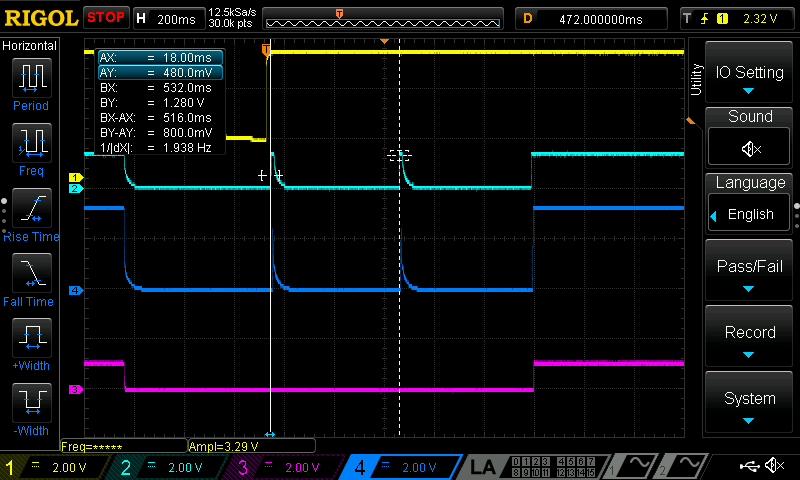

As you can see in above picture, it has 500ms between each retry to power DCDC4 (3.3V). For more information, I put a ocilloscope capture with detail view of this failure case.

Regarding to pcb layout, We follow the layout guidelines in datasheet: 47uF output capacitance and 1 mm of distance between pad and capacitor.

After that, we think new PMIC sillicon revision (D0) does not fix previous issues detected in -B0 revision. We have observed that some boards seem to start-up even after 8 retries. This performace generates a chained problems many components in our product, including ETH PHY.

My question is: What do you think what is the cause of this behavior? Is there any explanation or root cause for these retries?

Thanks in advance. Don't hesitate to ask any test that you need to solve this issue.

Best Regards.