Hi,

I previously asked a question in the following thread.

e2e.ti.com/.../850587

I would like to ask additional questions.

(Question1)

Is the timing of Tstrt starting immediately after VDD starts?

Or is it from the time when Vpor or VDD(min) is reached?

(Question2)

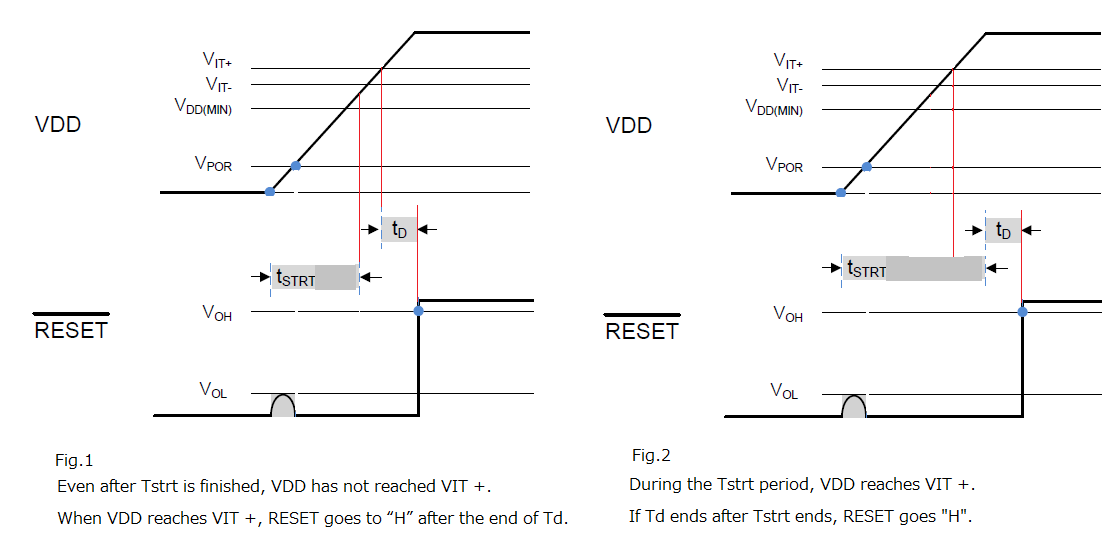

Are the contents of Fig.1 and Fig.2 below correct?

Best regards,