Other Parts Discussed in Thread: CSD19536KTT

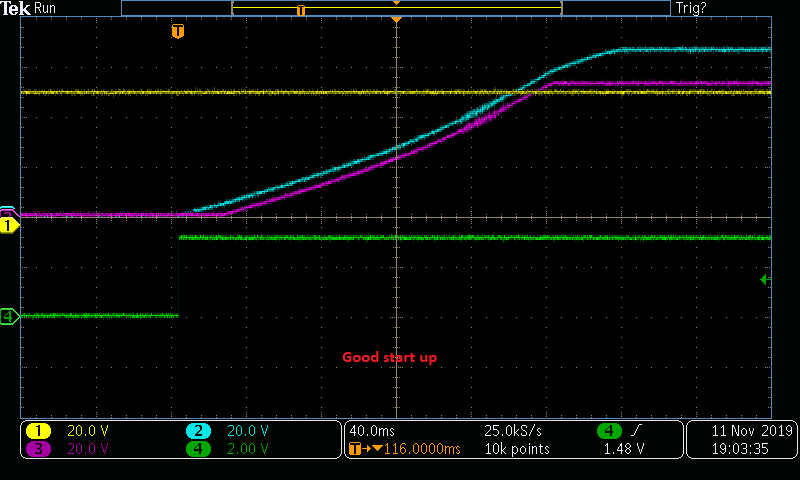

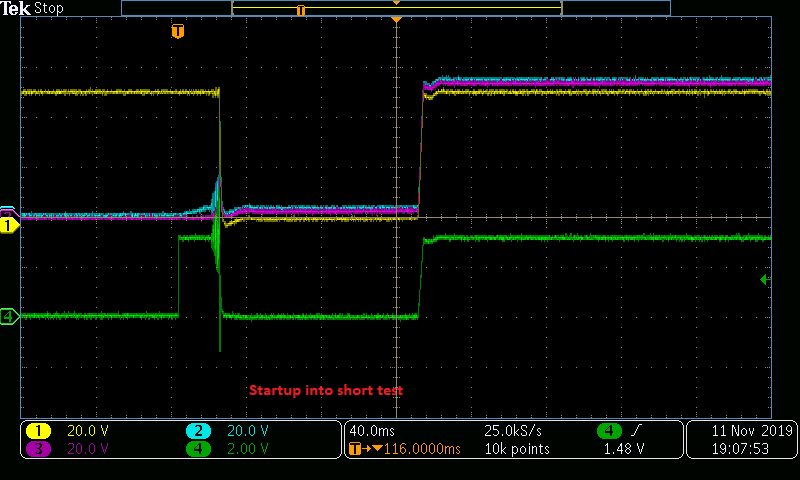

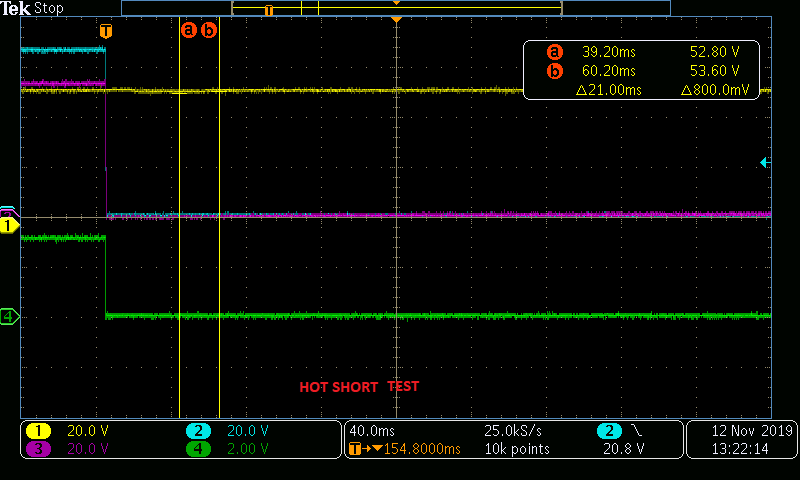

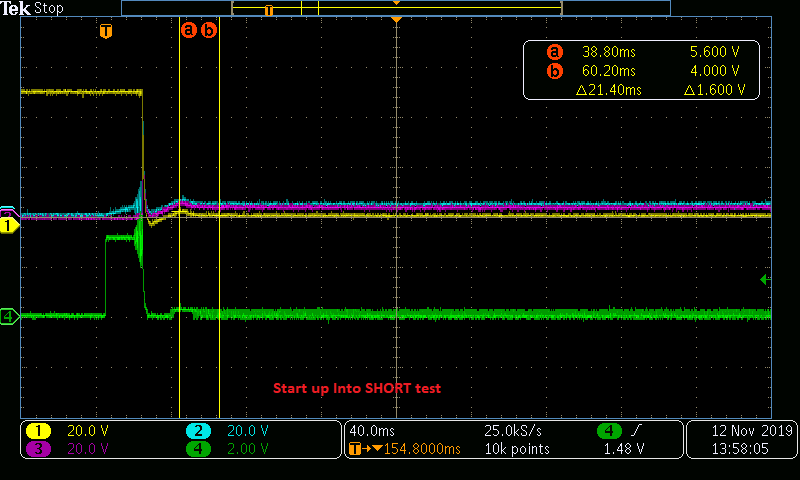

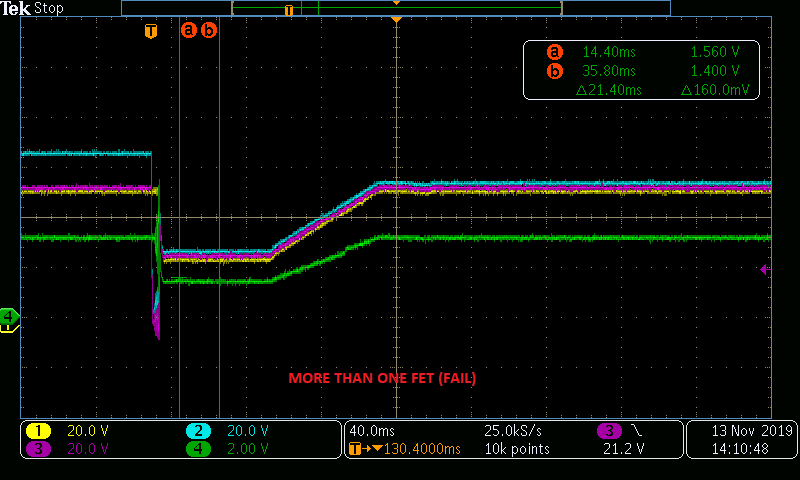

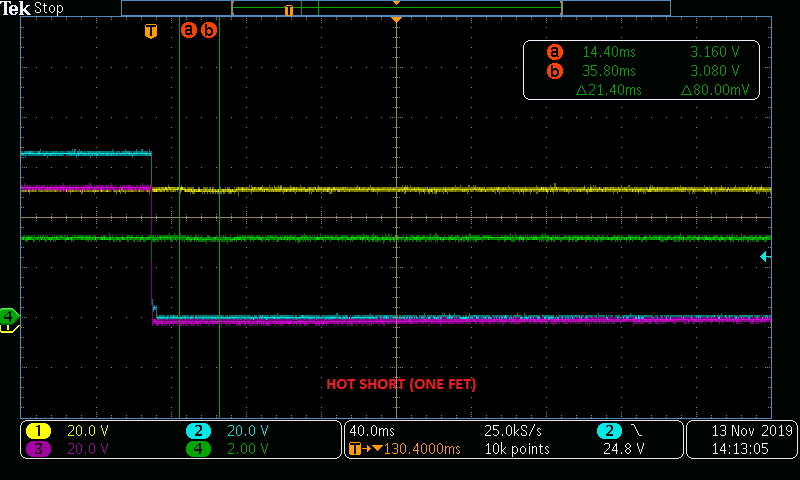

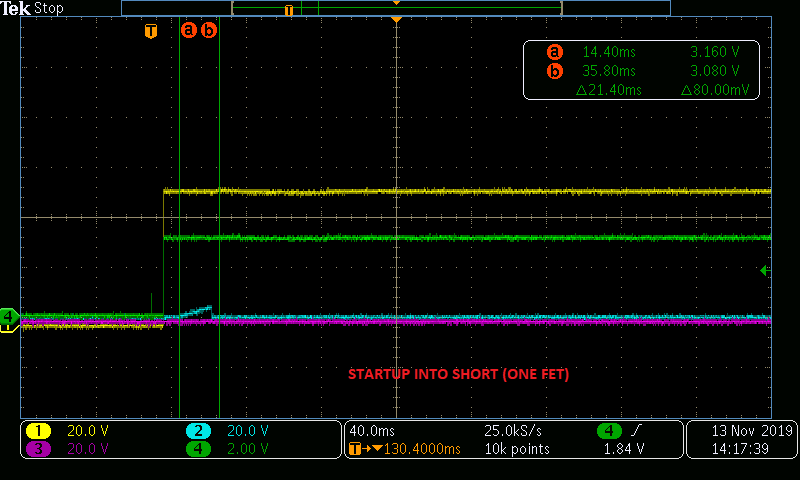

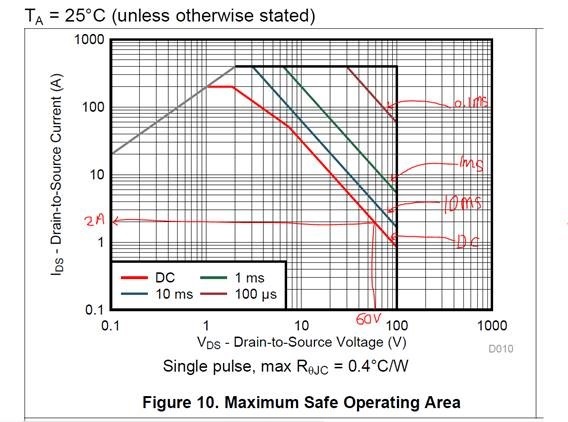

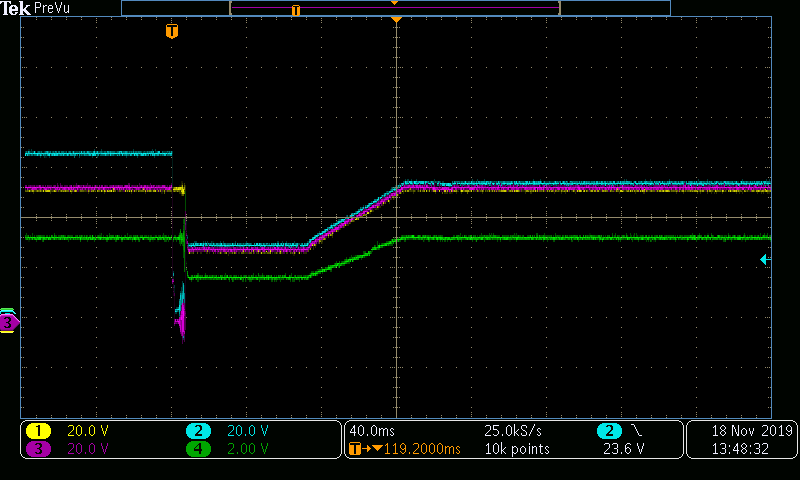

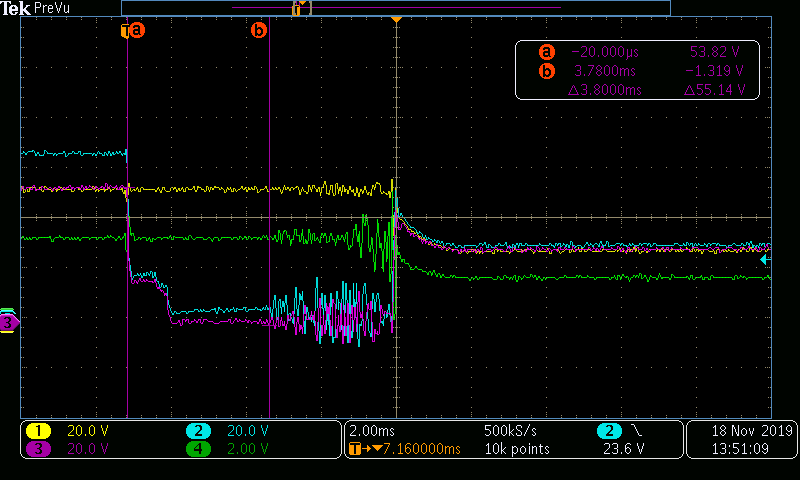

I am testing hotswap circuit (lm5066) for "startup into short". The output of the LM5066 is shorted then I enable the device. in a good case, LM5066 has to realize the huge current in a usec and Cicuit Breaker (CB) gets activated and hold the gate low and as a result shut down the output. however I am seeing that the power FET (CDS19536KTT) is burning when I run this test. below are the status of afew registers after the failhecking registers after fail:

D7h=00h

80h=10h

E1h=08BAh

Register D7 is 00h so no safety feature is disabled. register 80h, i see that the bit 7 (CB fault) is not even triggered.

Why the CB is not getting triggered?