Other Parts Discussed in Thread: UCC28951

Hi team,

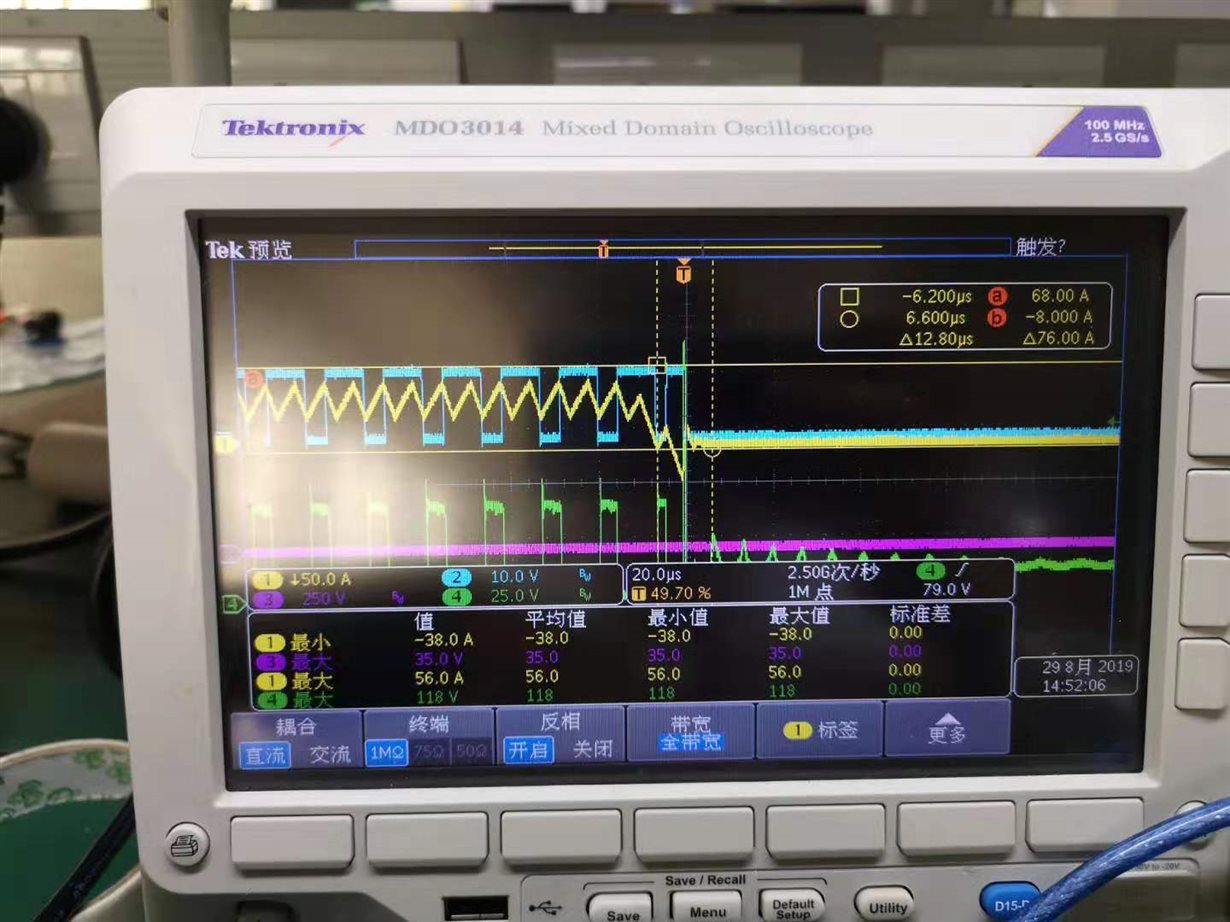

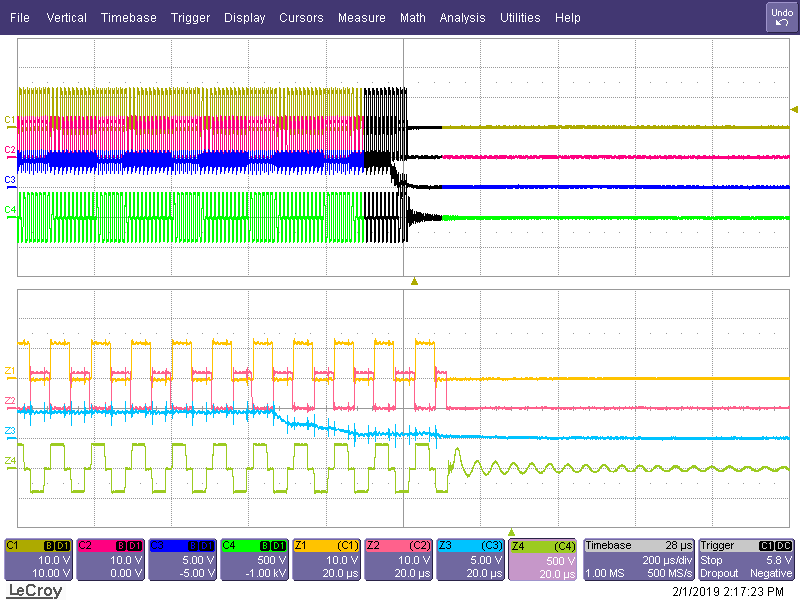

my customer use UCC28951-Q1 and have an issue is that when the shunt down, the duty cycle of Vds and gate driver signal will decrease ,please see the below picture.

The Blue is Synchronous rectifier driver signal, the Yellow is inductor current and the Green is Vds.

You can see that when the current goes down, the duty cycle of driver signal will decrease and there will have a overshoot on the VDS.

The problems are that:

1. why the duty cycle will decrease?

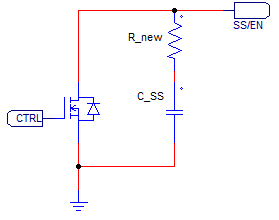

2. In customer application, when the pull low the SS/EN pin, the comp pin will also been low, we think it may cause the duty cycle change. So, they want to know what's the relationship between phase shift angle and comp pin voltage ? do you have more clearly description about this?

Thank you.