Hi

My customer has question.

The following is described in the explanation of the PG output of TPS82130.

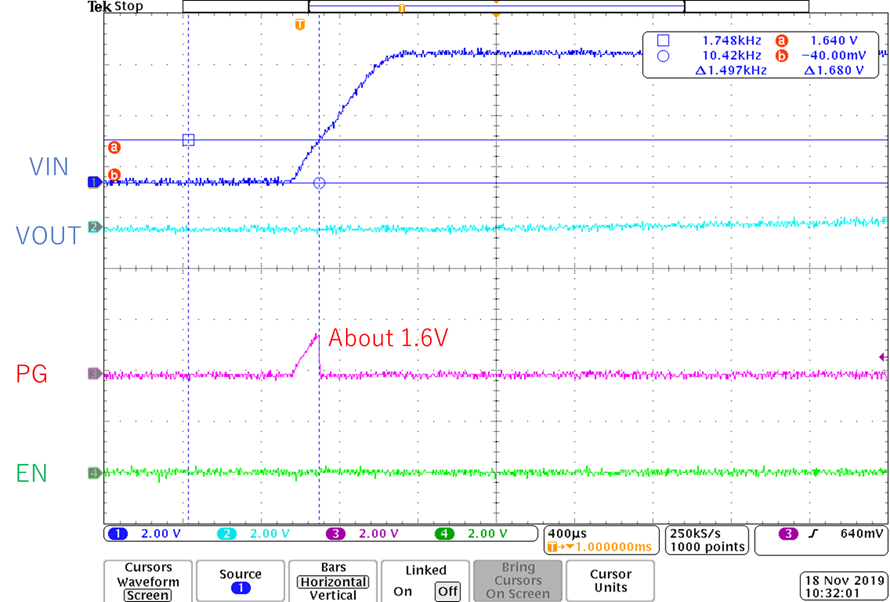

However, when the waveform is confirmed, PG falls to Low after the input voltage rises to about 1.6V.

The PG pull-up destination is the input voltage.

Probably there is a delay time, is this behavior correct?

If there is a delay time, how long is it?

Best Regard

T Kishi