Other Parts Discussed in Thread: LM5155, LM5022, PMP20676

Hi Richard,

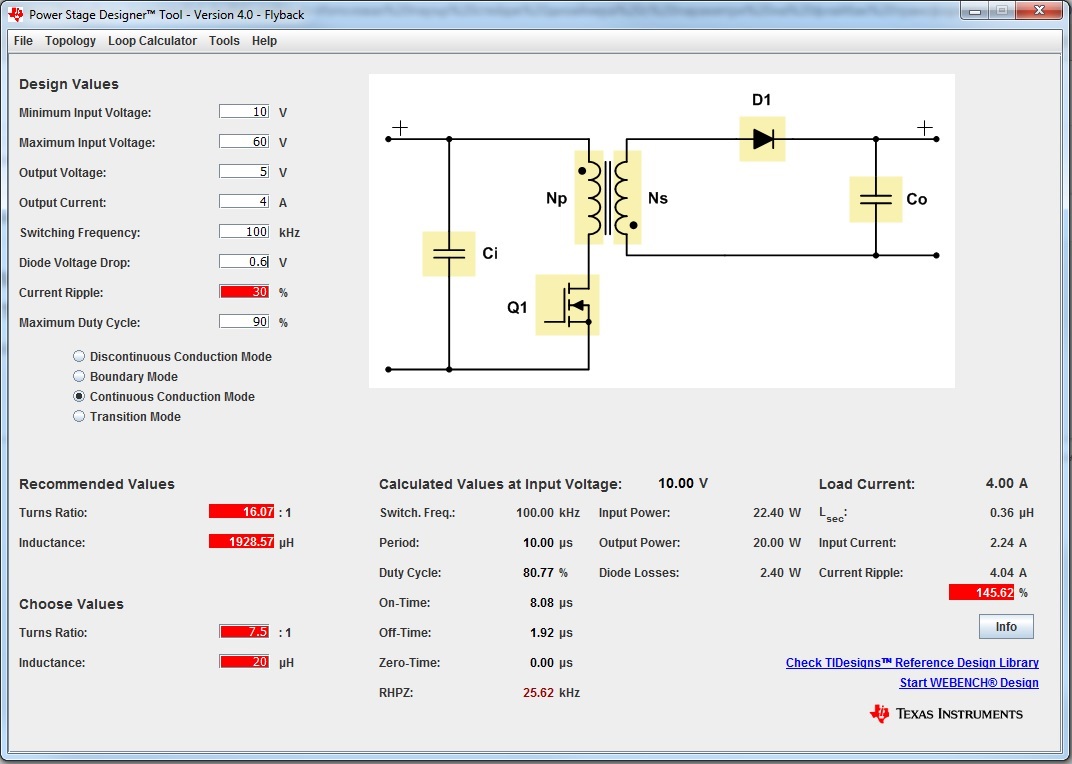

I used the Power Stage designer with parameters flaybak transformer 20 uH / 7,5:1 / 100kHz and got the following results:

My question is: Is it possible to design TPS40210 in this duty cycle?

Thanks,

Tsvetan