Hi TI

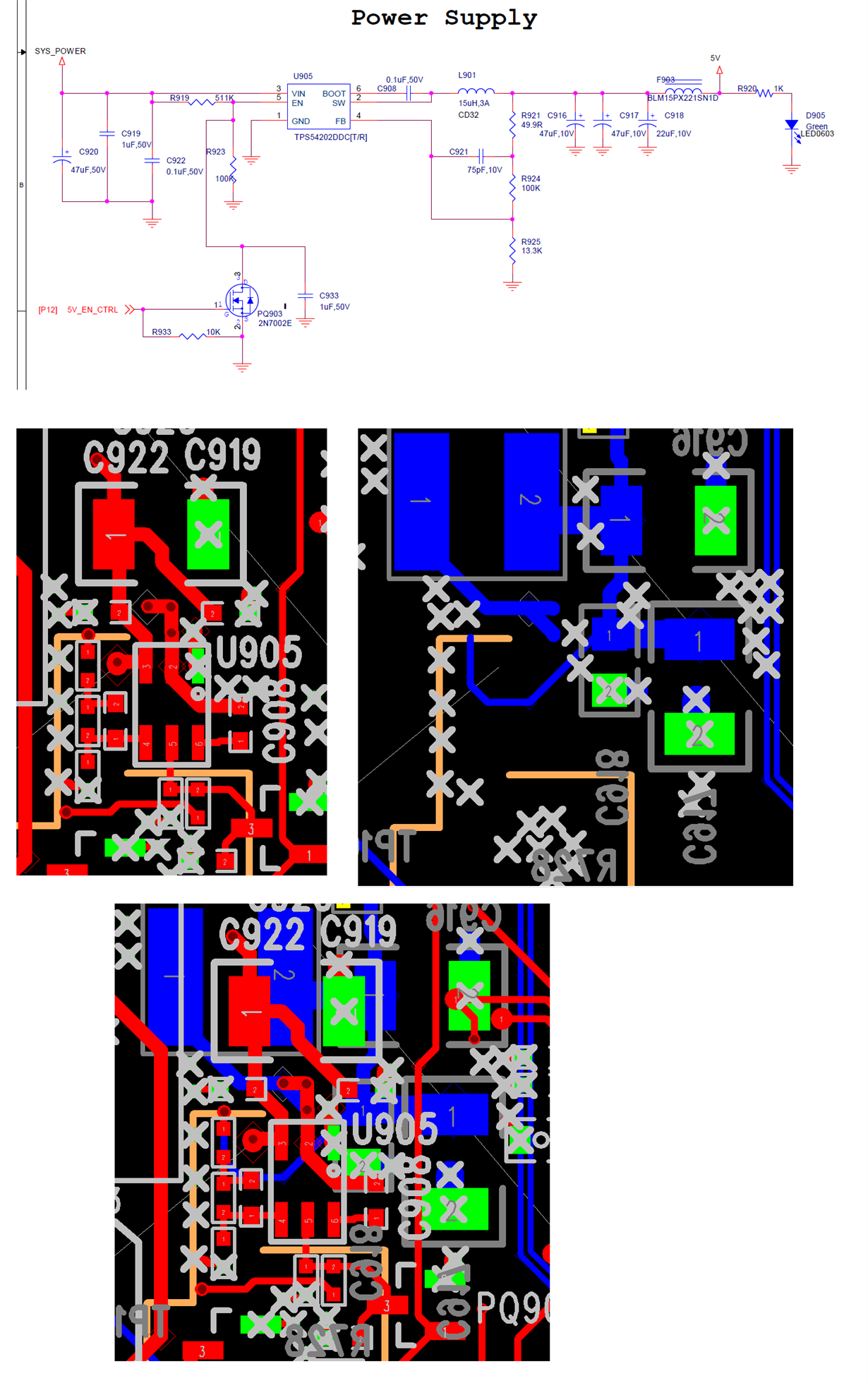

I use TPS54202 to buck from 24V to 5V with about 1A.

And now we see some failures that the VOUT and GND of TPS54202 is shorted immediately when 24V plug in sometimes.

this failue is not happened at the first Previous times, means those failure boards are worked before.

this failure is not happened when 24V is already power on. means those failure boards worked normally if 24V can power oon successfully at that time.

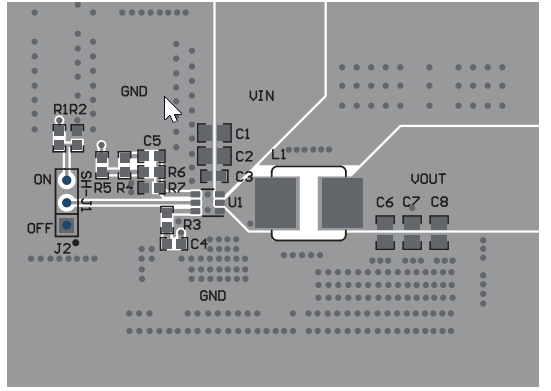

So, Could you please help me to check the schematic and layout below?

5V_EN_CTRL is always enable in this discussion.

the red is top layer and blue is bottom.

Thanks