Other Parts Discussed in Thread: CSD87381P, BOOSTXL-TPS650861, CSD87331Q3D, IPG-UI, USB2ANY

Dear expert,

Months ago, thanks to your help, we found the soldering issue for our TPS650864 evaluation board through this thread https://e2e.ti.com/support/power-management/f/196/t/875459. After re-soldering the board, we got the new board.

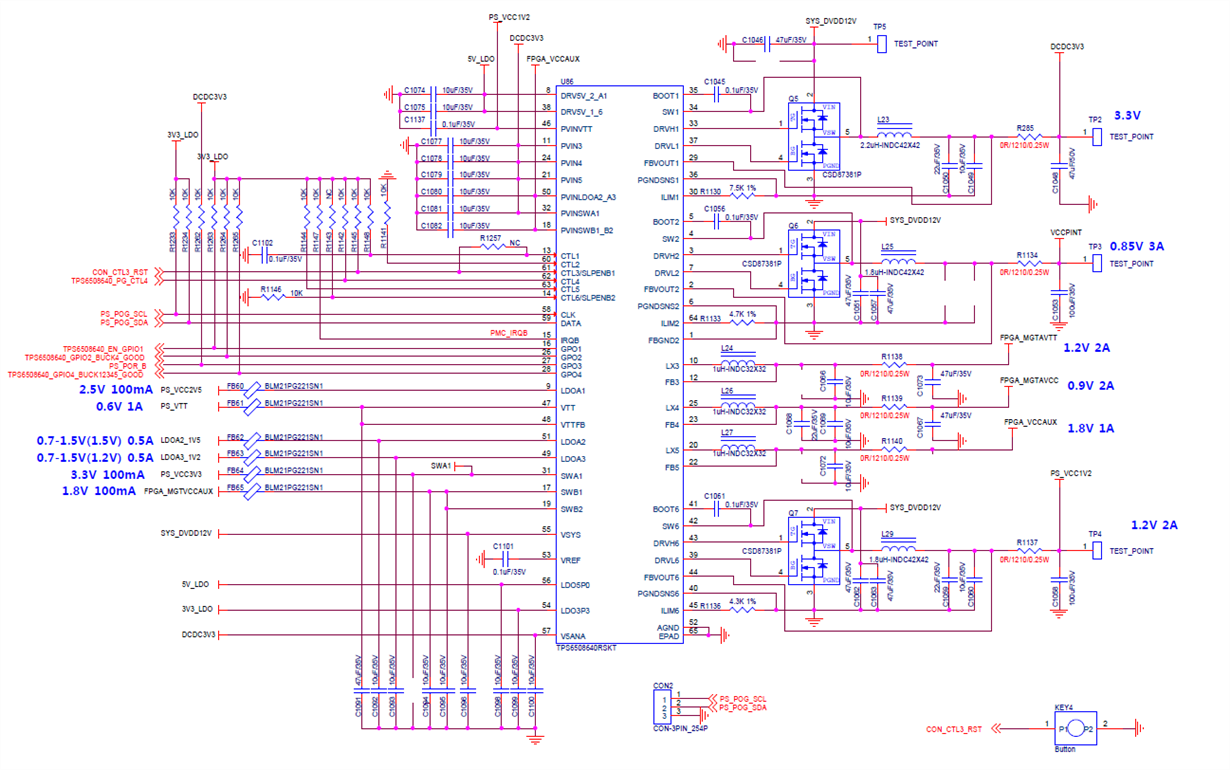

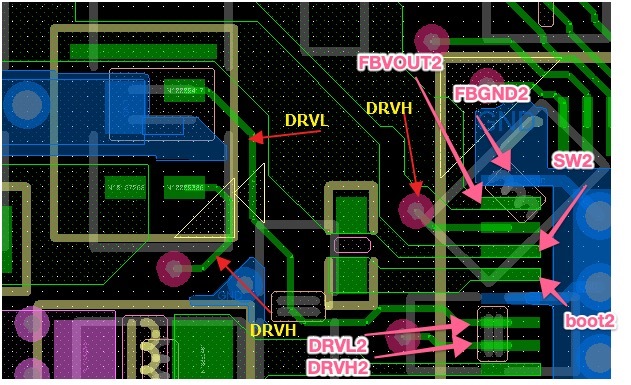

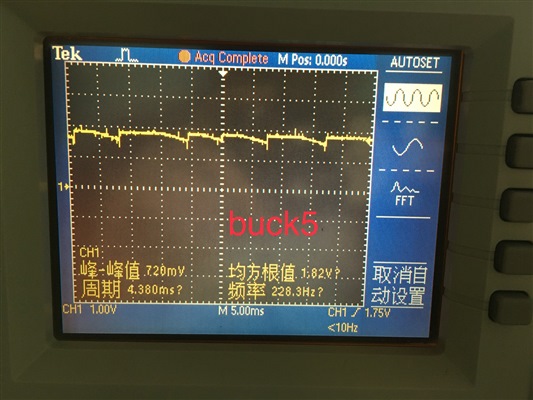

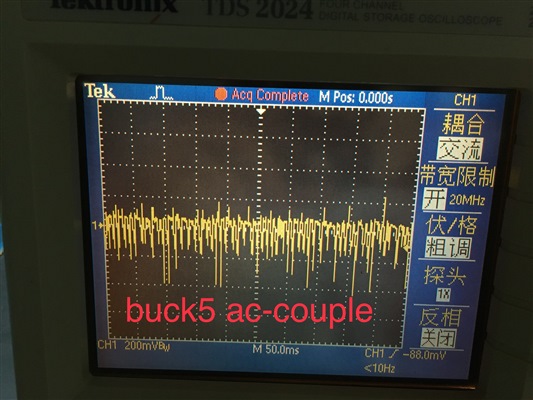

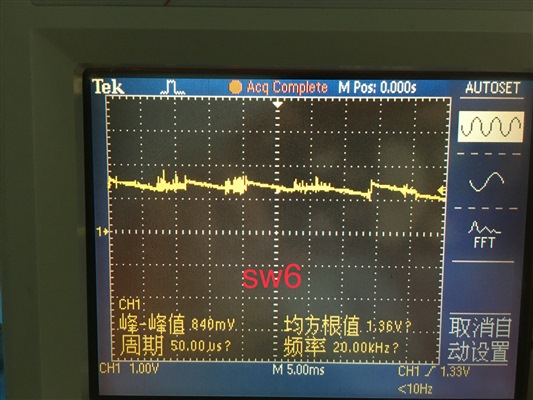

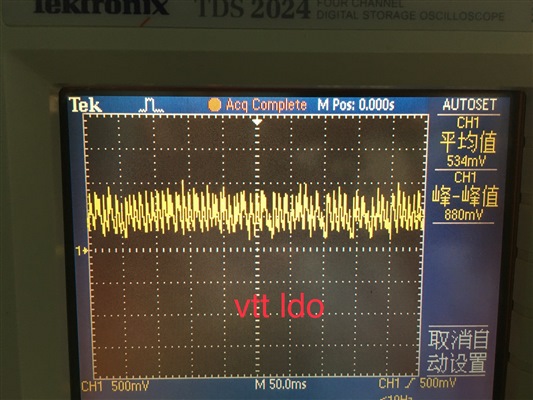

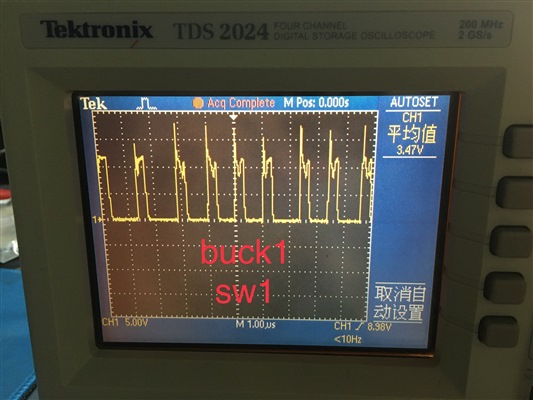

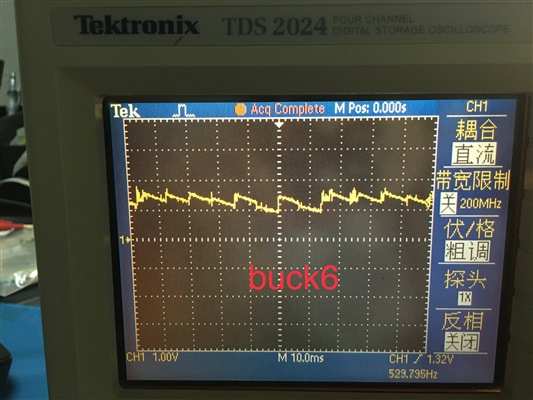

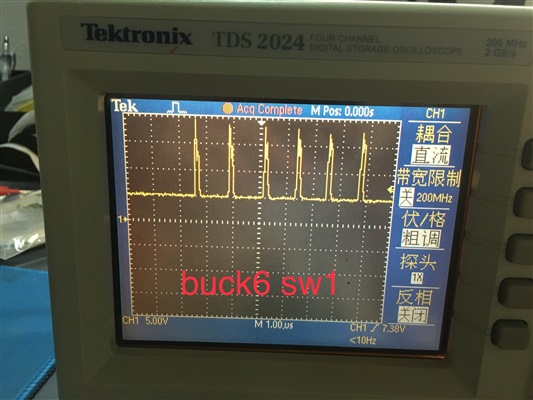

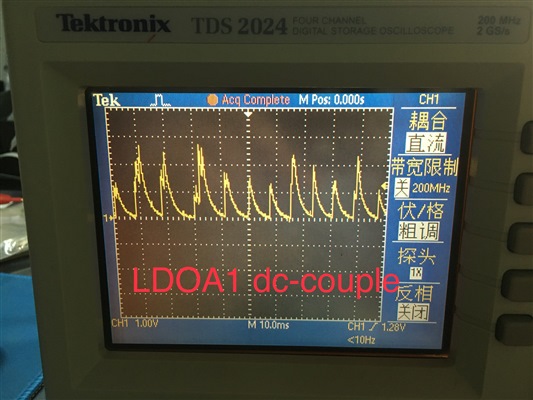

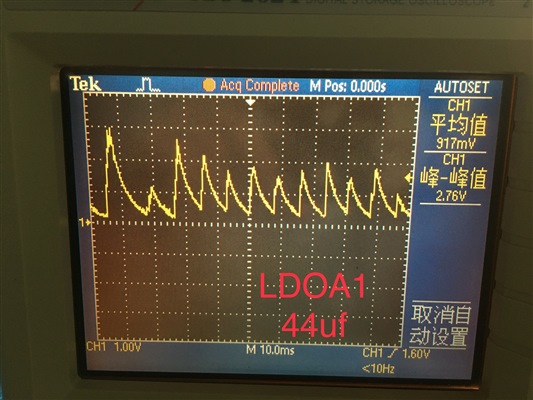

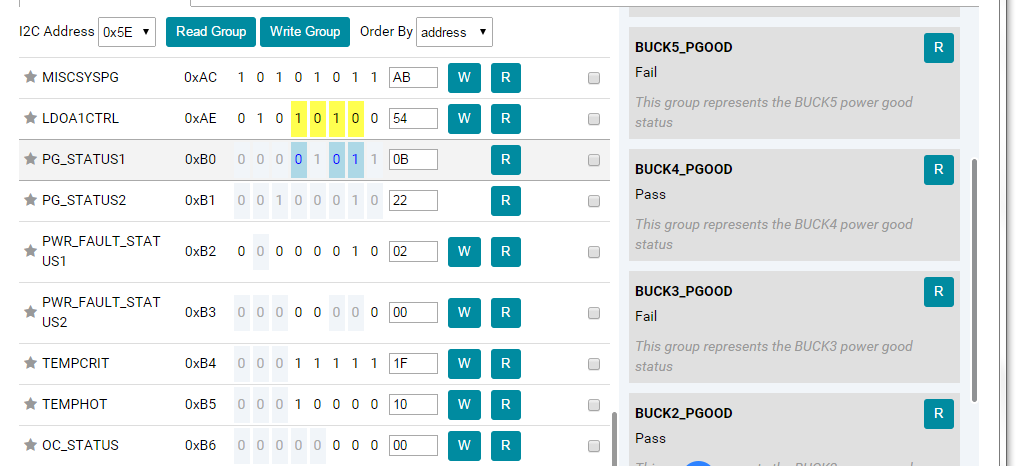

In the test, LDO5V5, and LDO3V3 are both correct. When probing the SW2 output, which is expected to give 0.85V, it seems not to work correctly. The output voltage is not stable, jumping from 0.5V to 4V, back and forth and the total current varies from 0.1A to 0.4A with the input voltage being 12V. And the chip is kind of hot. Due to the SW2 unnormal state, the other power rails have no output.

My questions are as follows:

1. What factors may lead to SW2 unnormal state? As a newbie to the TPS650864 chip, any advice is welcome.

2. If we would like to cut off the SW2 and let the other power rails work, how to achieve it? We had a try, in order to make SW1 work, pull high on CTL4 alone, but it does not work.

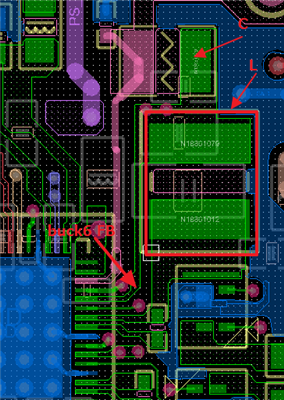

3. Could you help to check the circuits about SW2 as the following schematic?

Thanks ahead