Hi there,

we are considering use TPS7a4701 as tracking LDO in this thread (

), some questions to consult.

Vin = 14.4V(battery) or 19V(adaptor), Vout = Vin-0.3V.

Question1: For its current limit behavior : suppose during test we intentionally set a large CONSTANT I_load of 5A, we would see the I_out be limited to 1.26A(typical) according to section 7.3.1 in datasheet, and I assume the Vout will drop drastically. As time pass, 4701 will became hotter and finnally trigger its thermal shutdown. After shutdown it will become cooler, and when temp cools down below 150°C, it will work again but still in overload situation if 5A load is still ON. As this cycle goes on, the device will eventually damaged because of overheat. Is this perception correct ?

Question2: The load current is not constant vaule but intermittent pulse wave. average current is less than 1A , but the peak transient current could be as high as 4.5~5A .

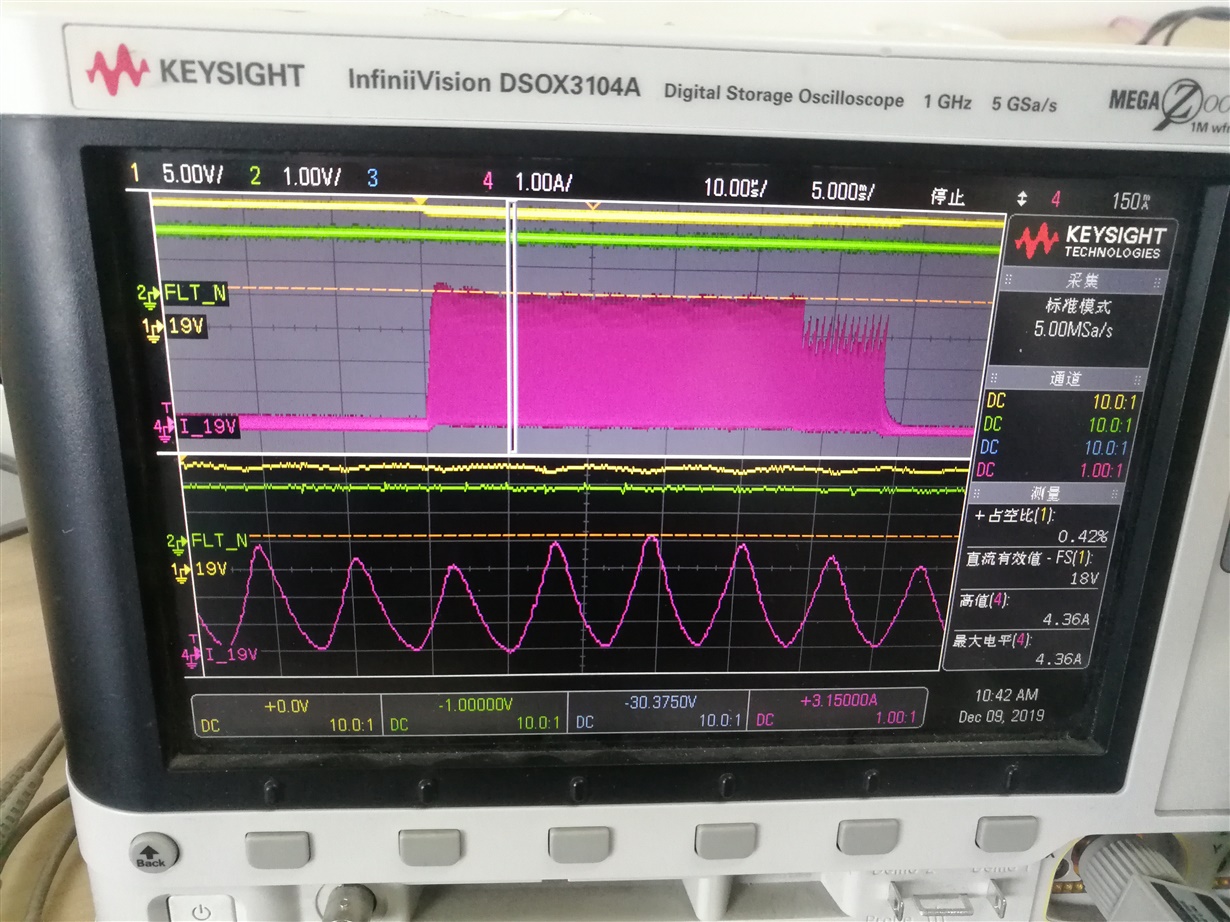

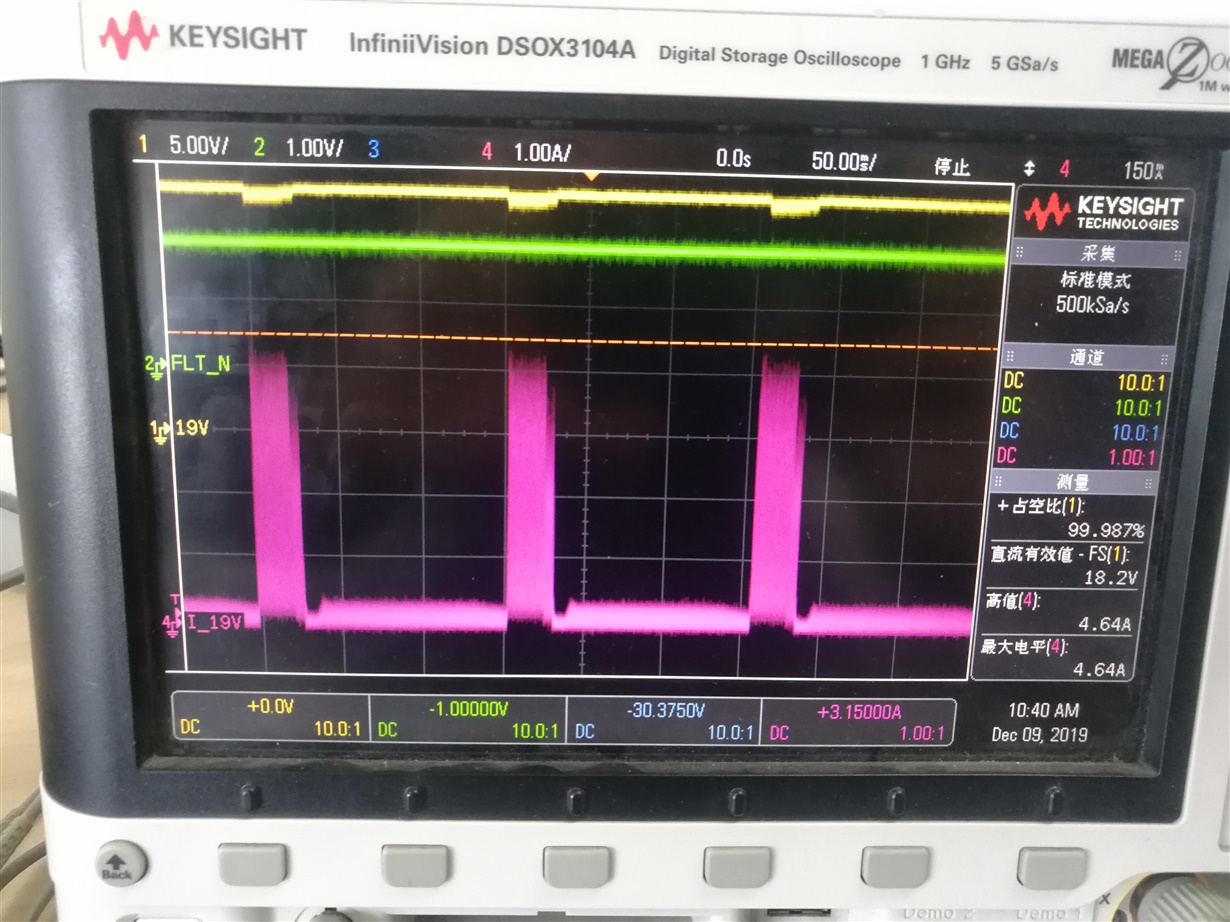

From pic1, you can see in 150ms peorid there is 125ms I_load = 0 and 25 ms I_load is rippling as pic 2(zoom in) shows, the ripple cycle in every 25ms is about 12us and nearly 5A.

I am concerned and not sure whether 4701 would be able to respond in time? or how fast (how short the current spike lasts) could 4901 response? We will have to test on board, but it would be better if TI has relevant data or info to reference.

Pic1. Current waveform Channel4

Pic2. zoomed in waveform (more details)

Thanks !!