Other Parts Discussed in Thread: UCC21520, , UCC28951

Hi,

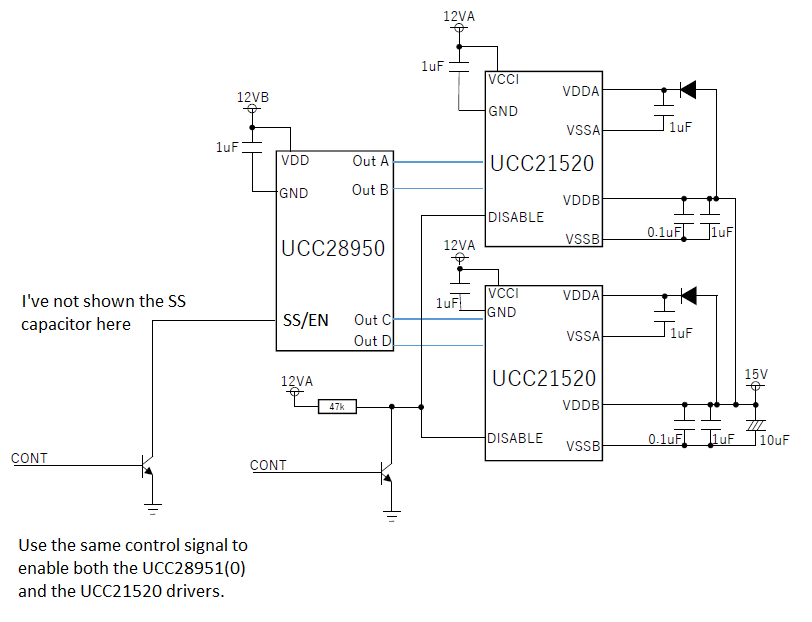

I'm considering a circuit using the UCC28950 and UCC21520 devices.

A schematic circuit and sequence are shown in the attached material.

I first thought of the PLAN1 circuit. However, due to the relationship with other circuits, VDD of UCC21520 is applied first.

Therefore, I am concerned that it may cause malfunction of the circuit.

Therefore, like PLAN2, I am considering adding a control circuit using Disable.

Is the PLAN2 circuit and sequence good?

In that case, should the UCC21520's Disable release timing be the timing when VDD of UCC28950 becomes 7.3V or more?

Best regards,UCC28950 and UCC21520 circuits and sequences.pdf