Other Parts Discussed in Thread: TPS7A4501EVM-385, TPS7A45, TPS7A47, TLV767

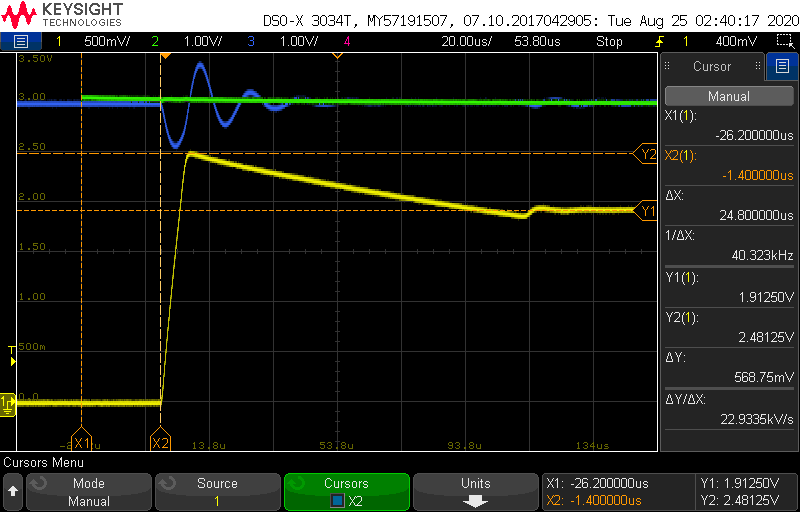

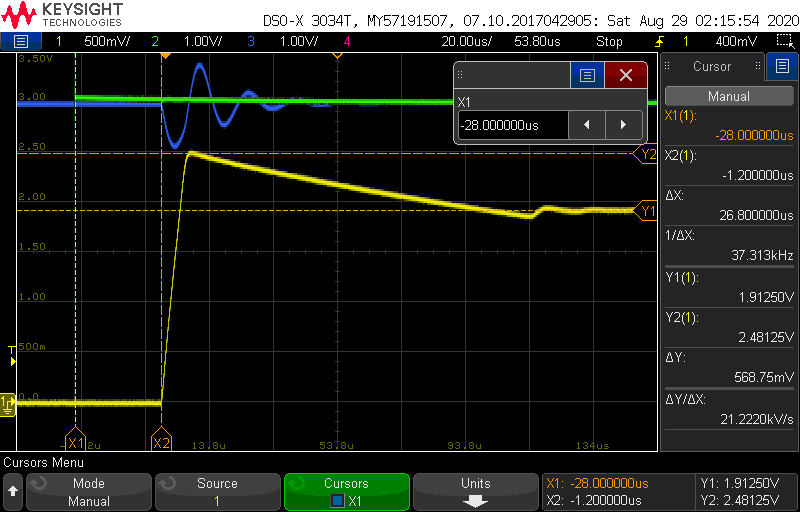

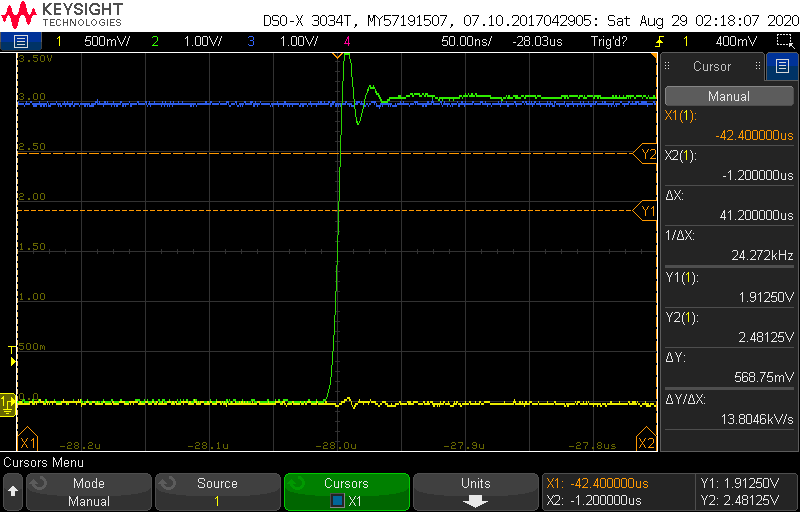

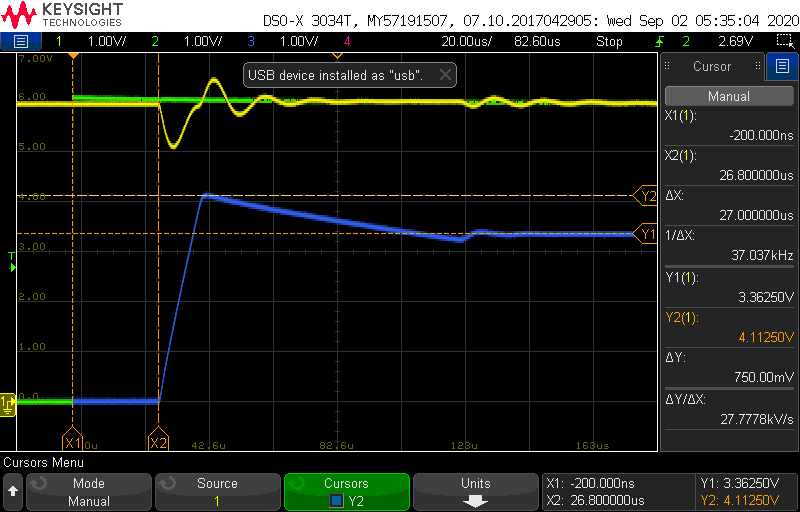

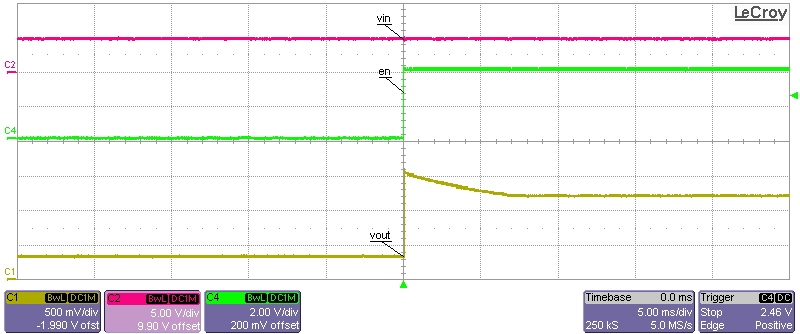

I'm experiencing the same overshoot issue when taking the TPS7A4501 out of reset. I can't recreate it in the TINA simulator though. What feedback was given to the original question I tagged to start this thread.

Thanks,

Nathan