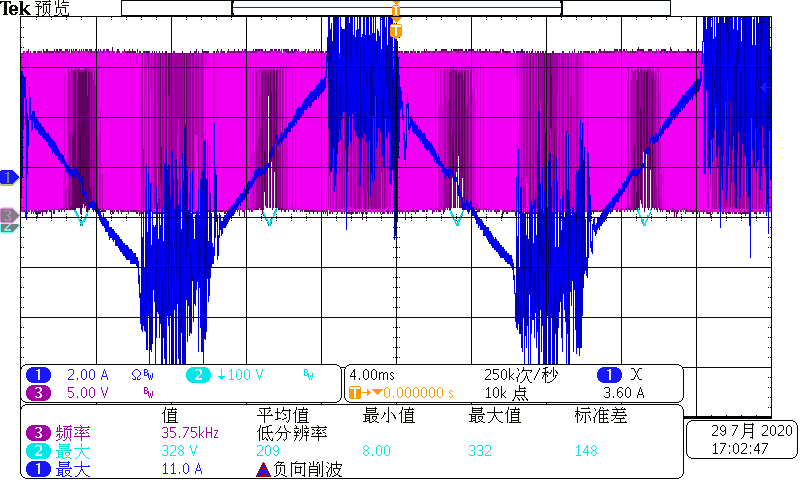

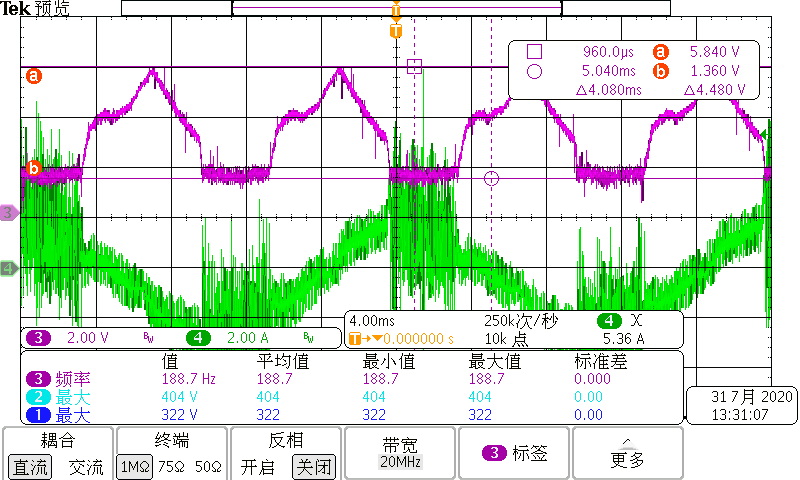

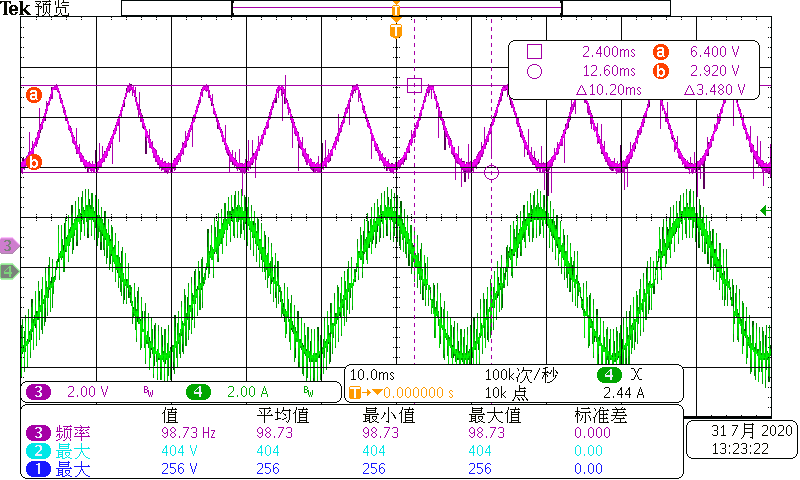

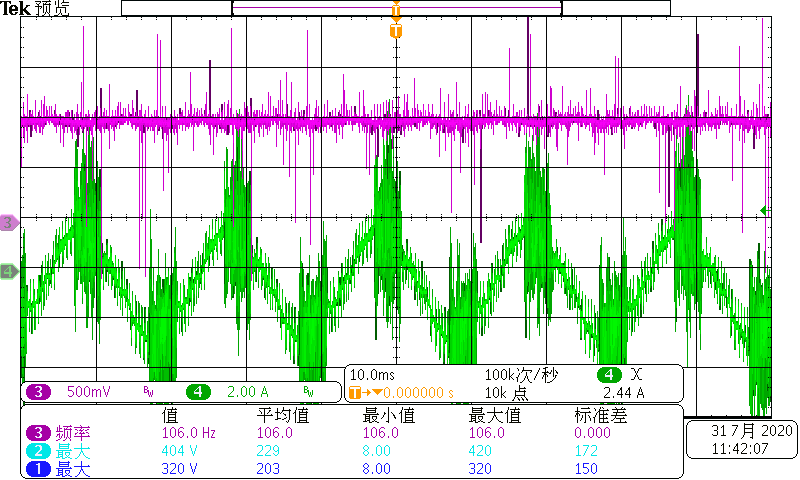

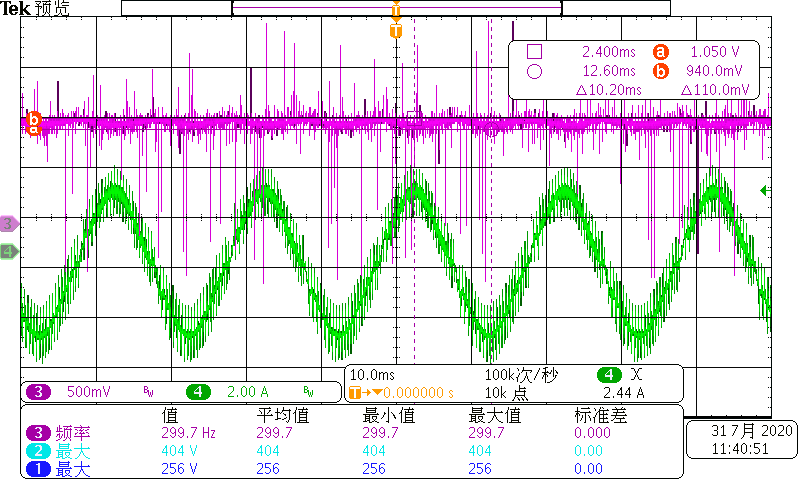

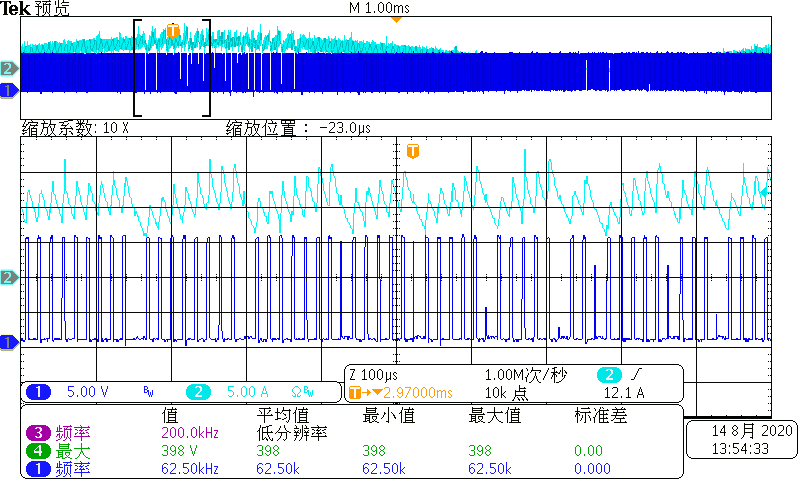

I cannot get the ideal PF, I designed a 3kilowat PFC, but when I added load to 1KW, the PF was 0.94.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.