Other Parts Discussed in Thread: TINA-TI, PMP8787

Hi,

Hope you are doing good.

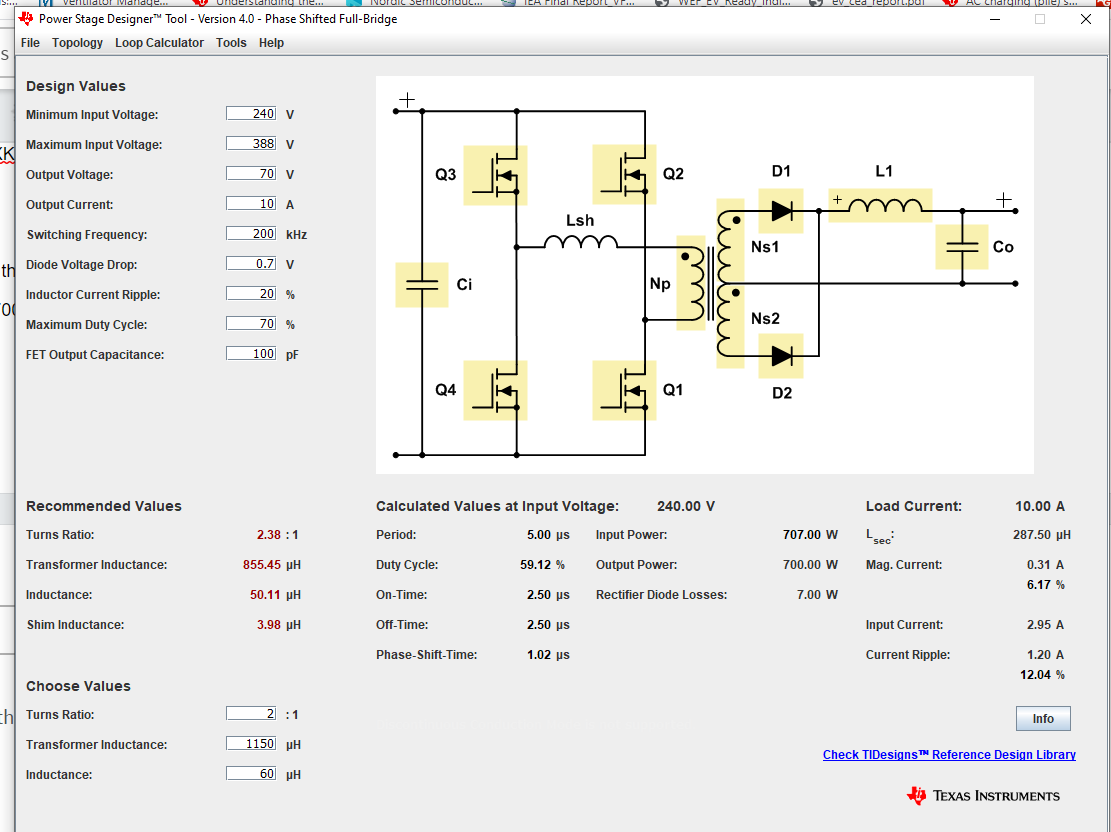

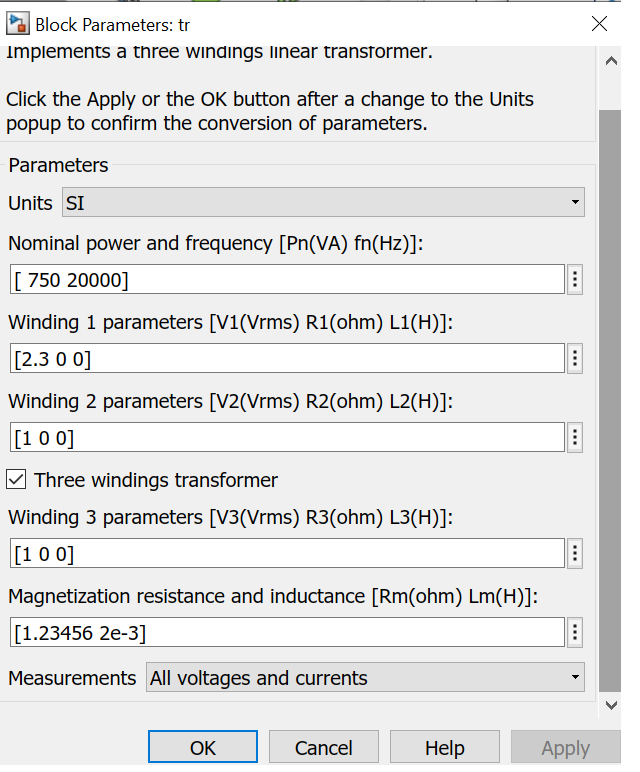

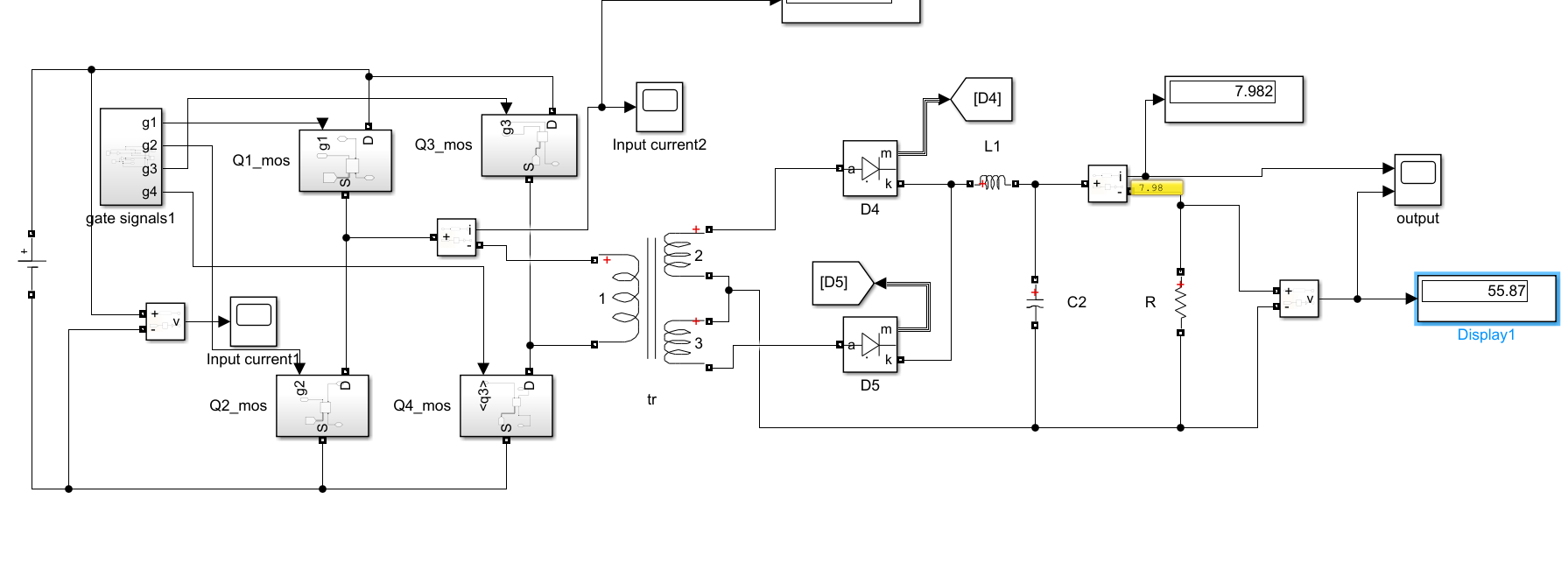

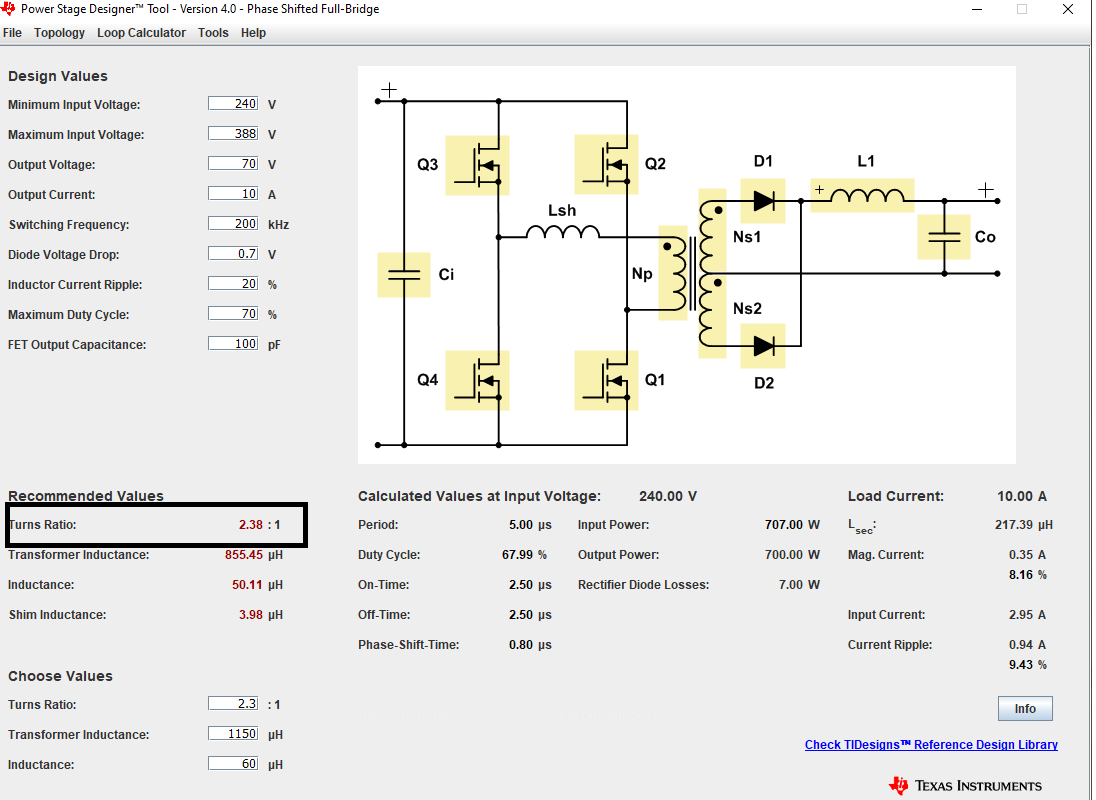

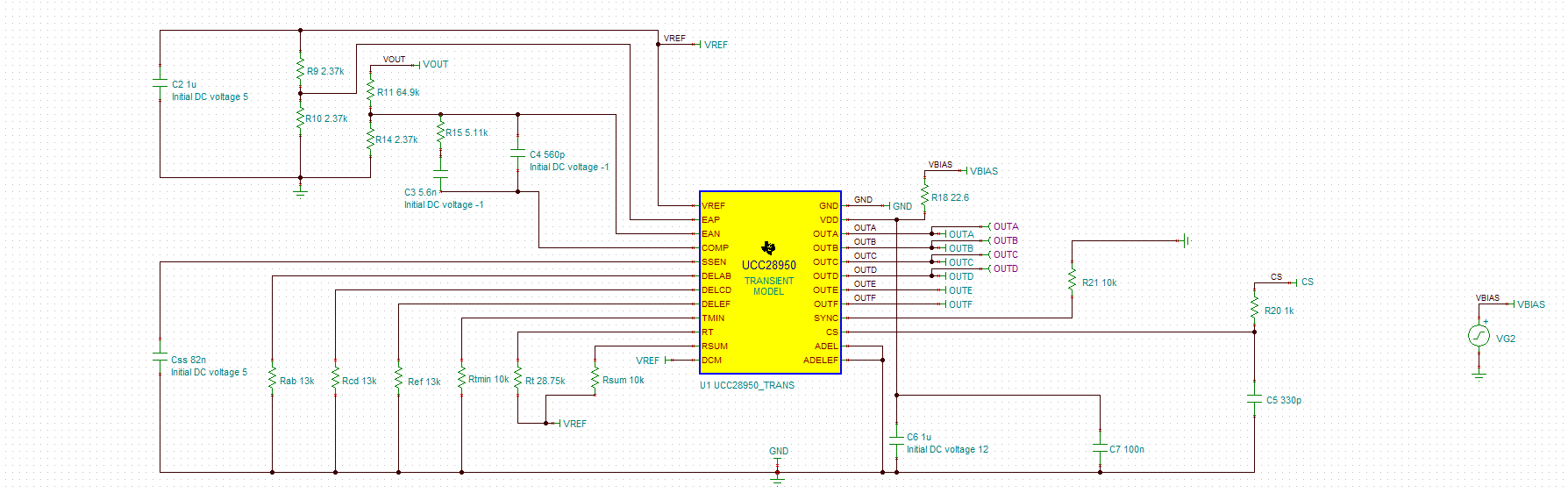

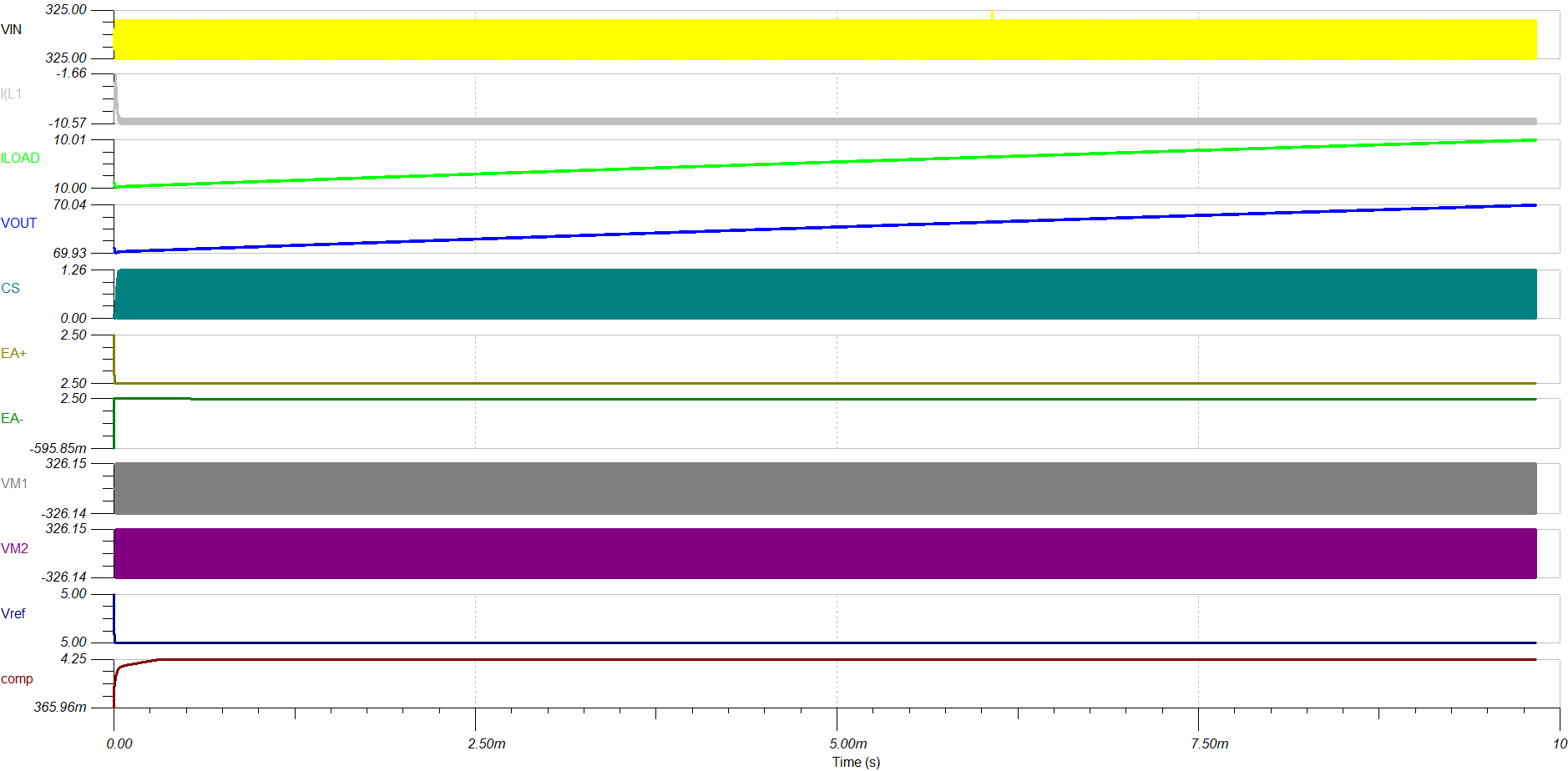

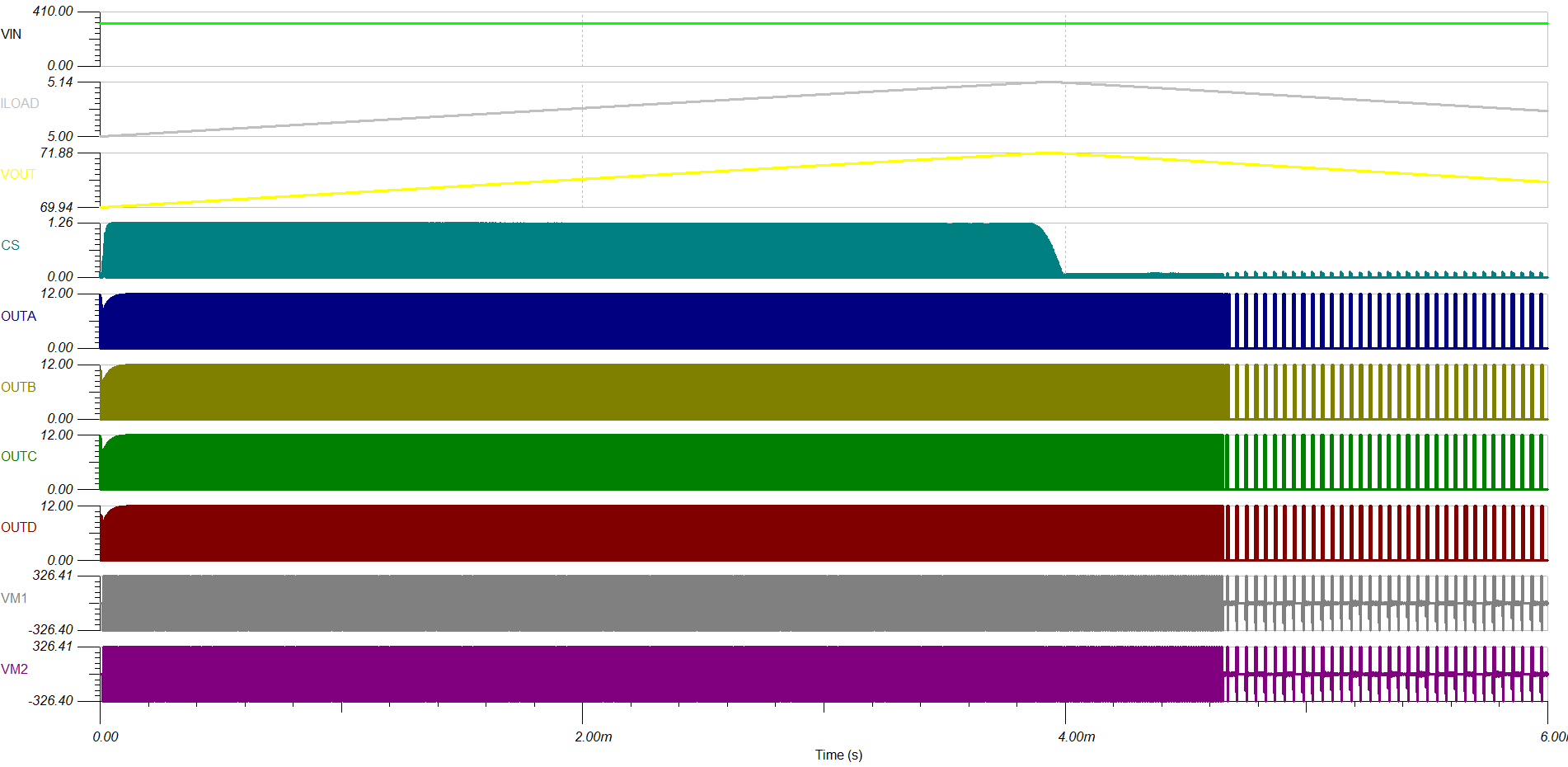

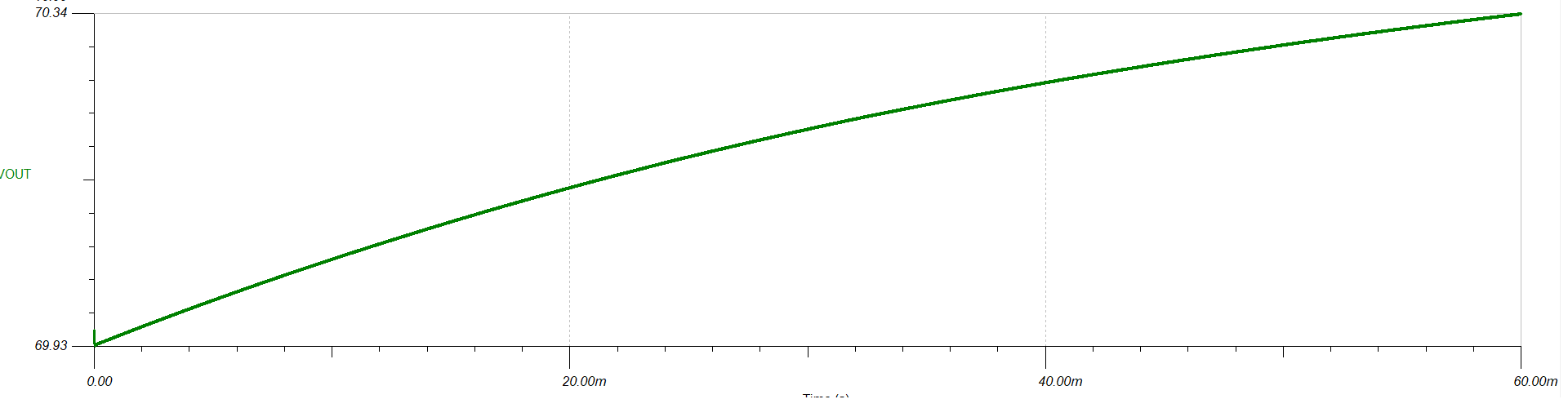

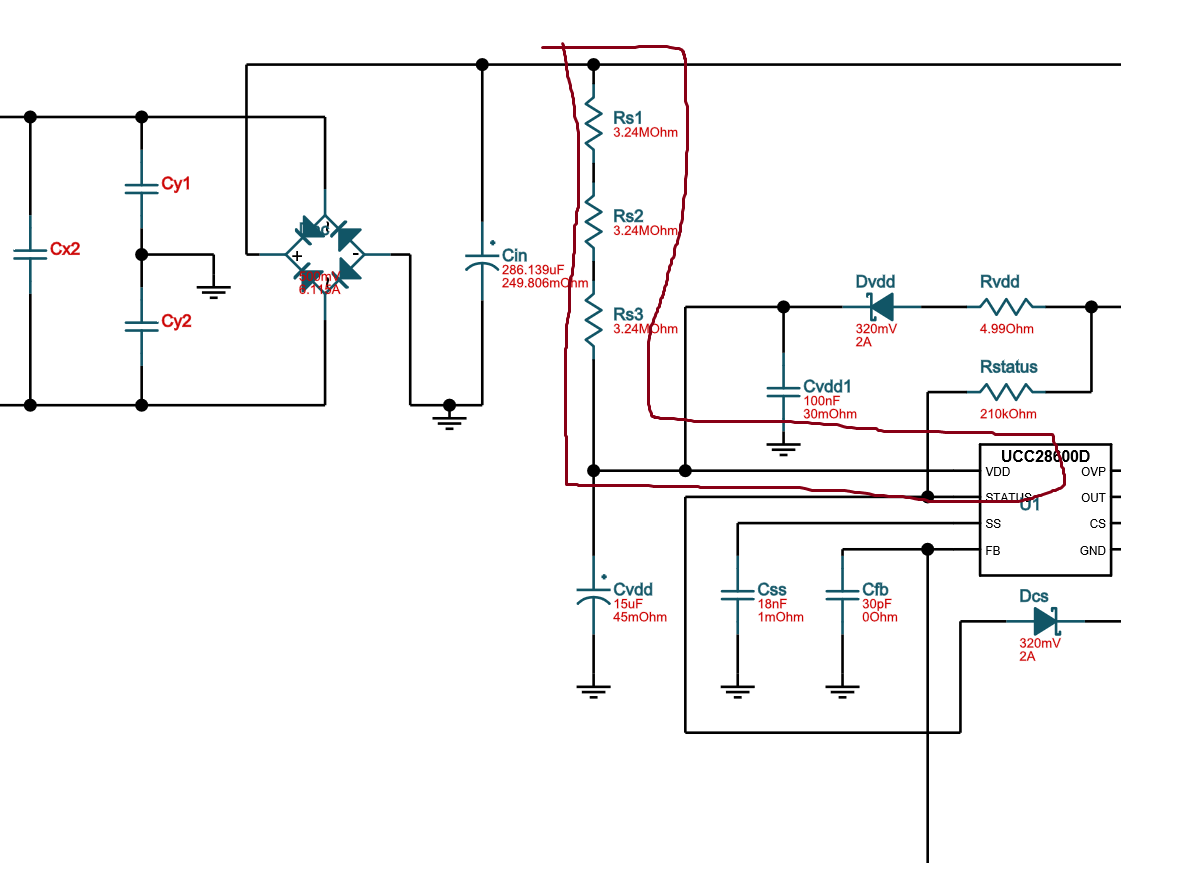

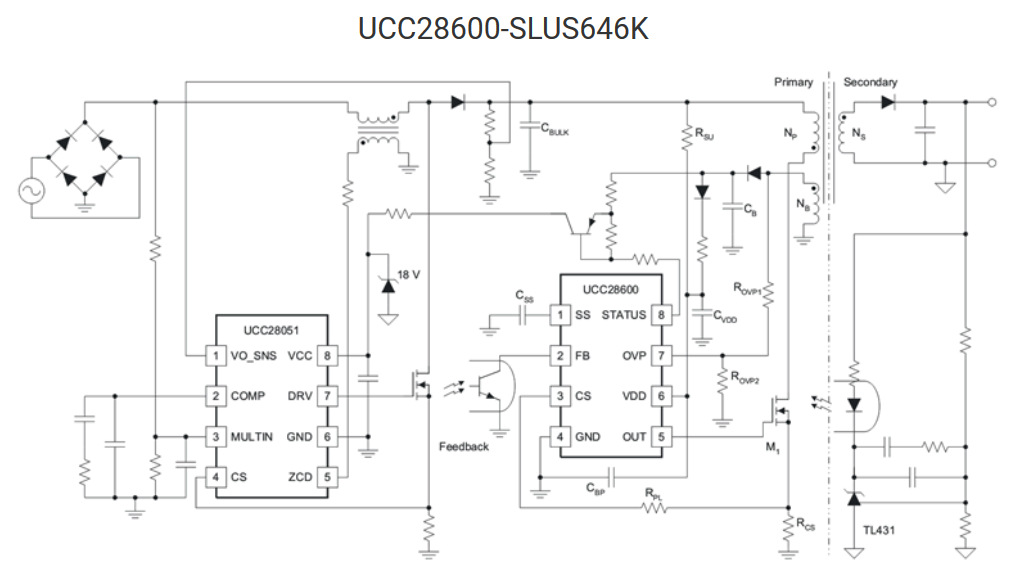

We are following SLUA560C reference design to design a 70V DC, 10A, 700 W smps with input of 170V to 275 V AC.

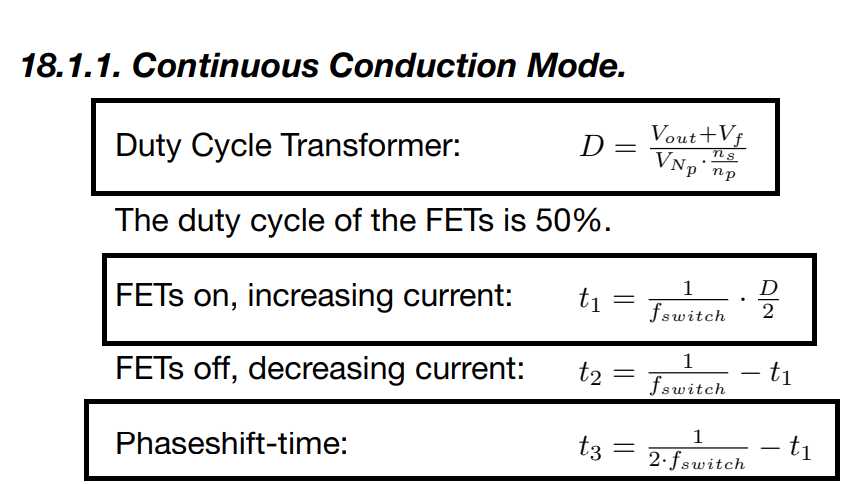

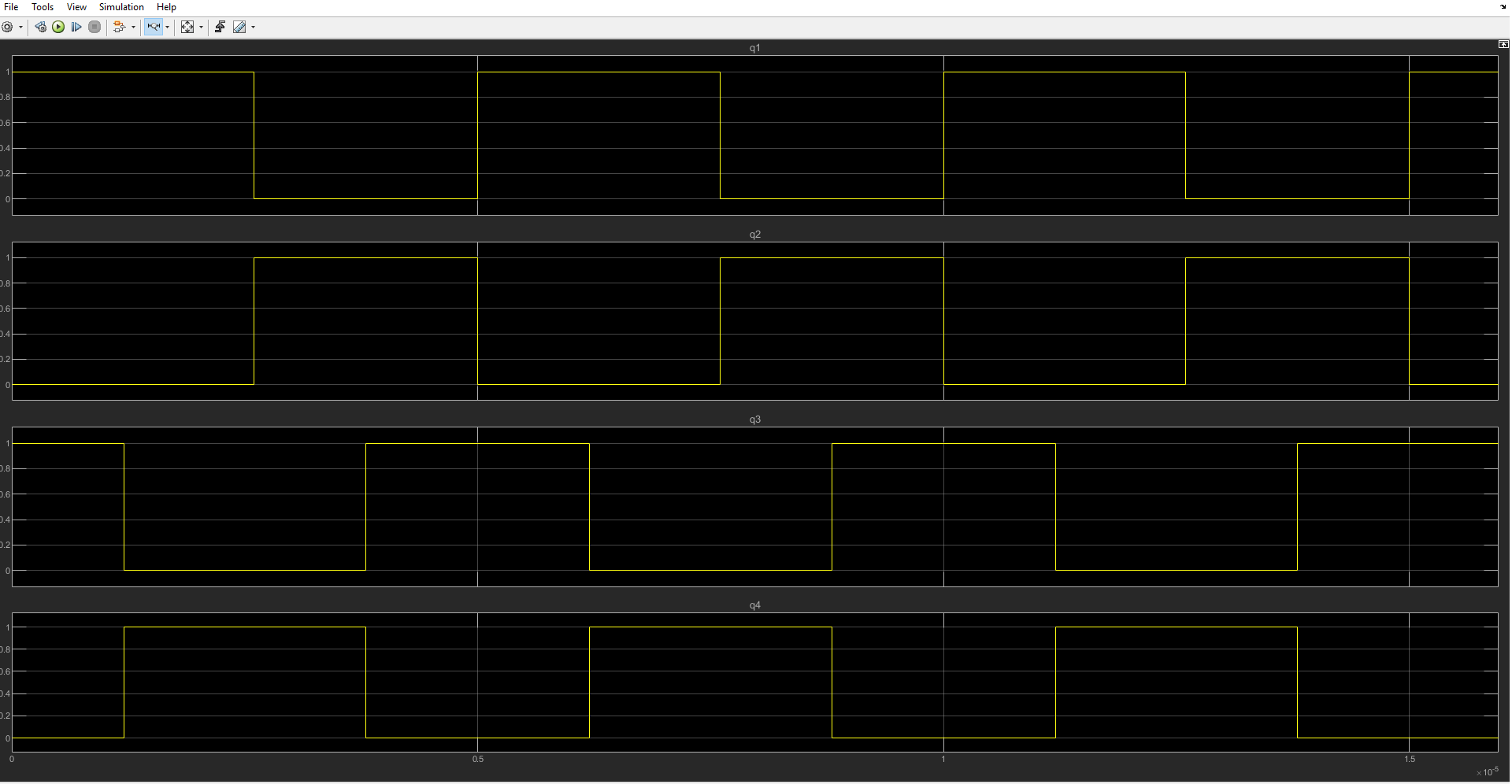

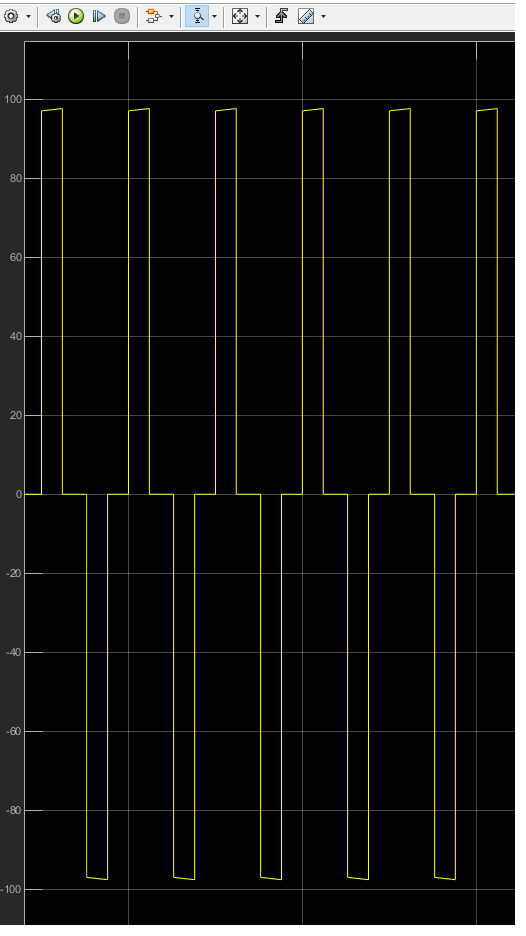

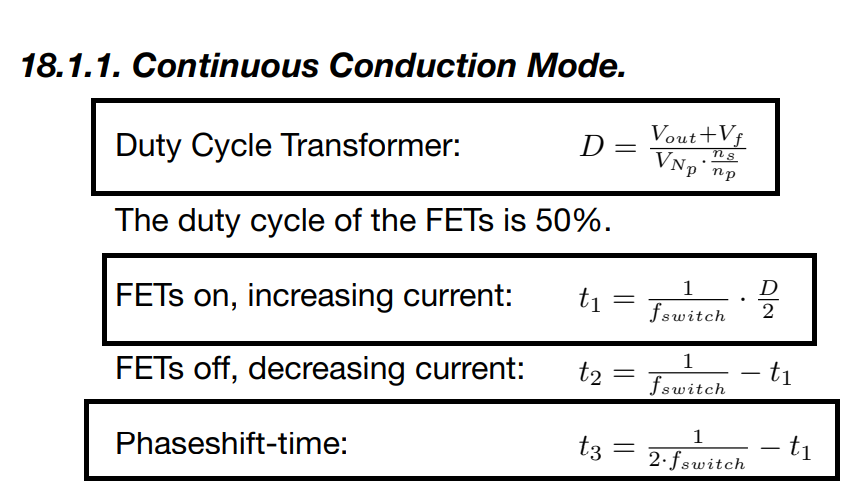

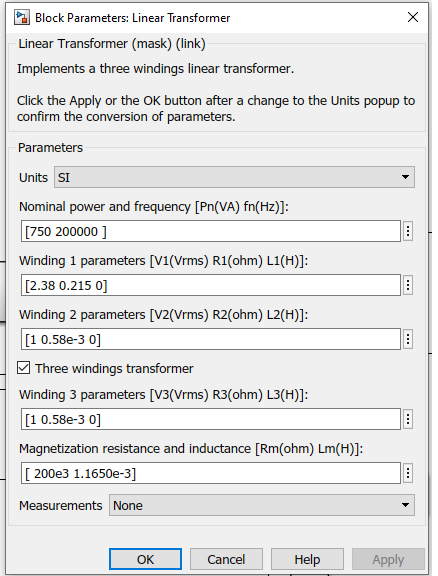

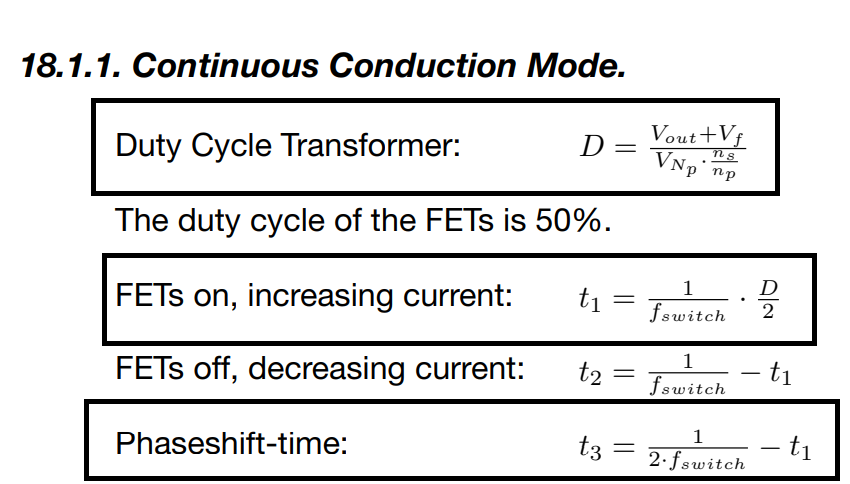

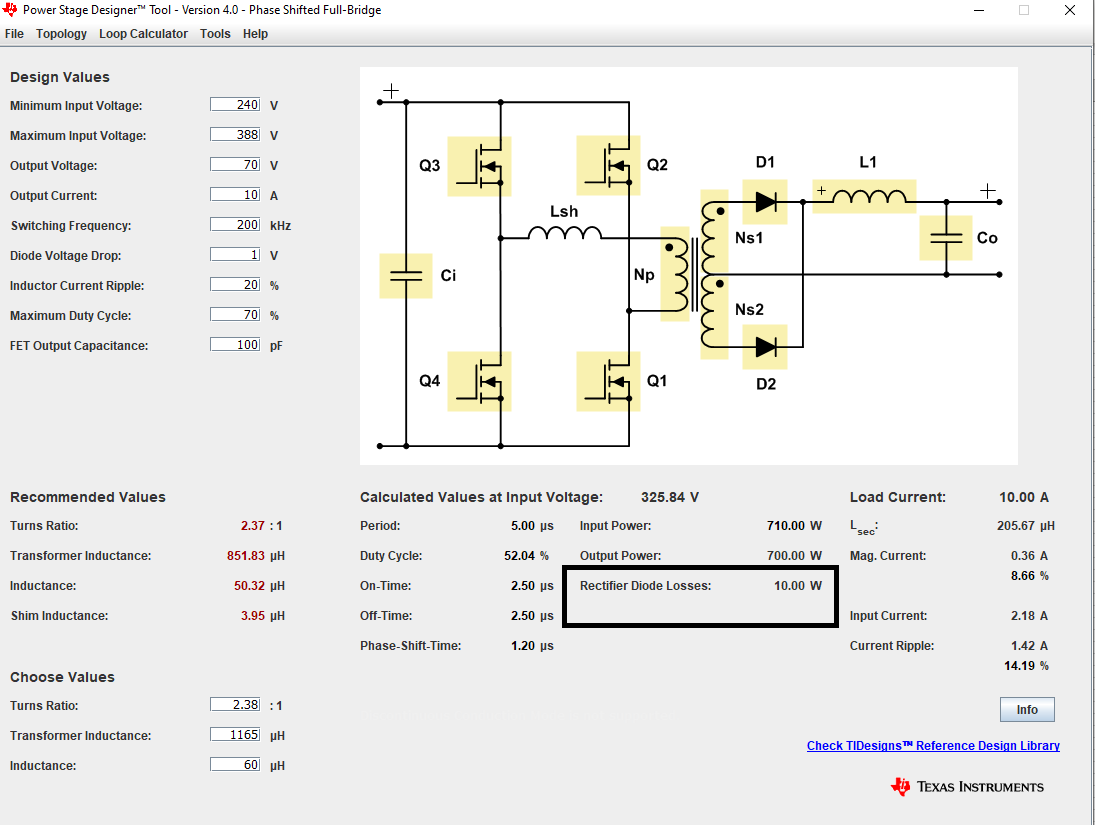

at the same time we are using power stage designer tool for phase shift full bridge design.

In the power stage design tool, on the primary side, there are 2 diodes where as on the SLUA560C there are two mosets.

We are trying to design the SMPS with 94% efficiency.

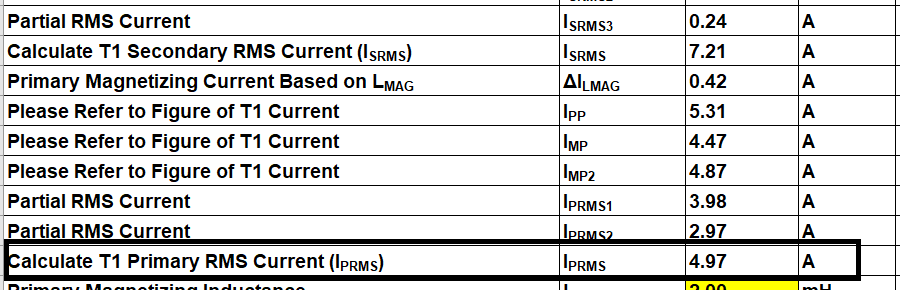

when it comes to the selection of components and the Pbudget calculations,

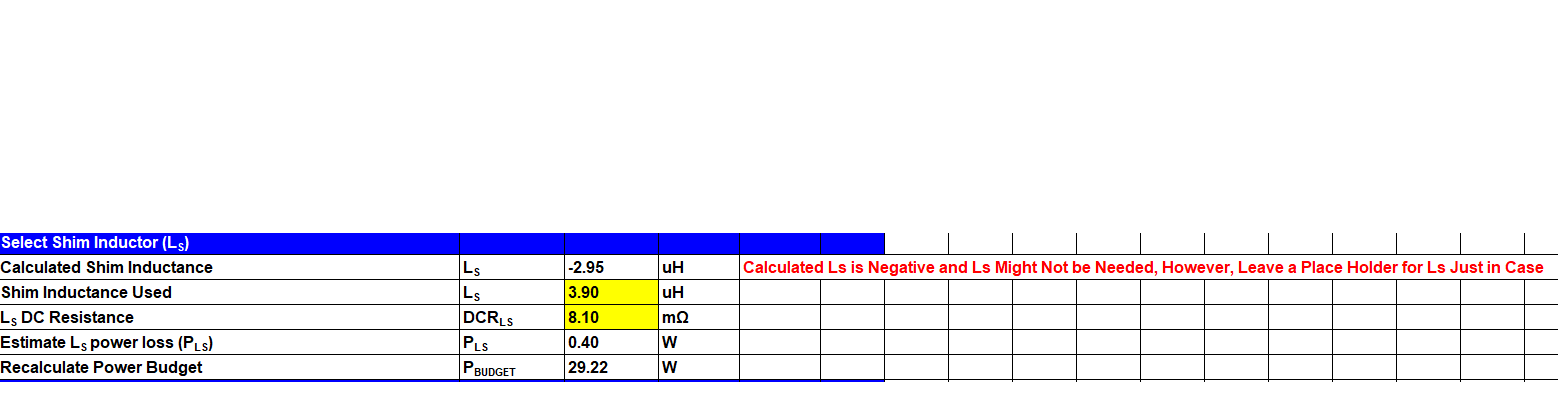

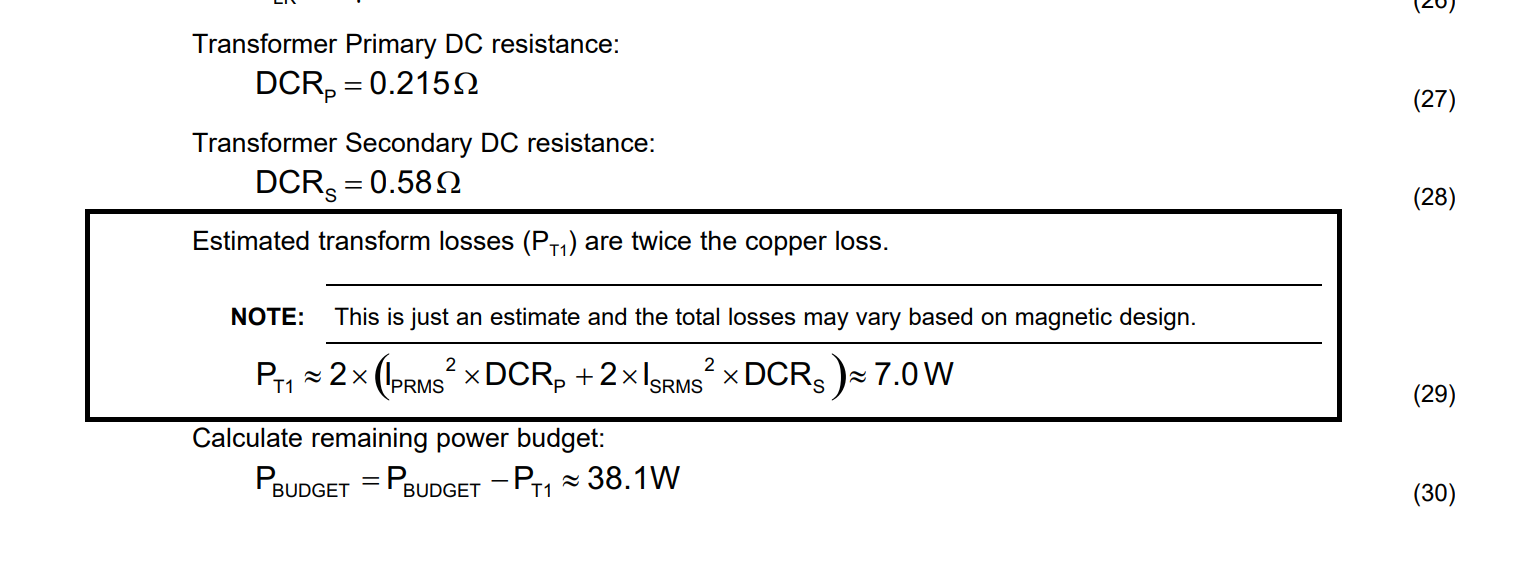

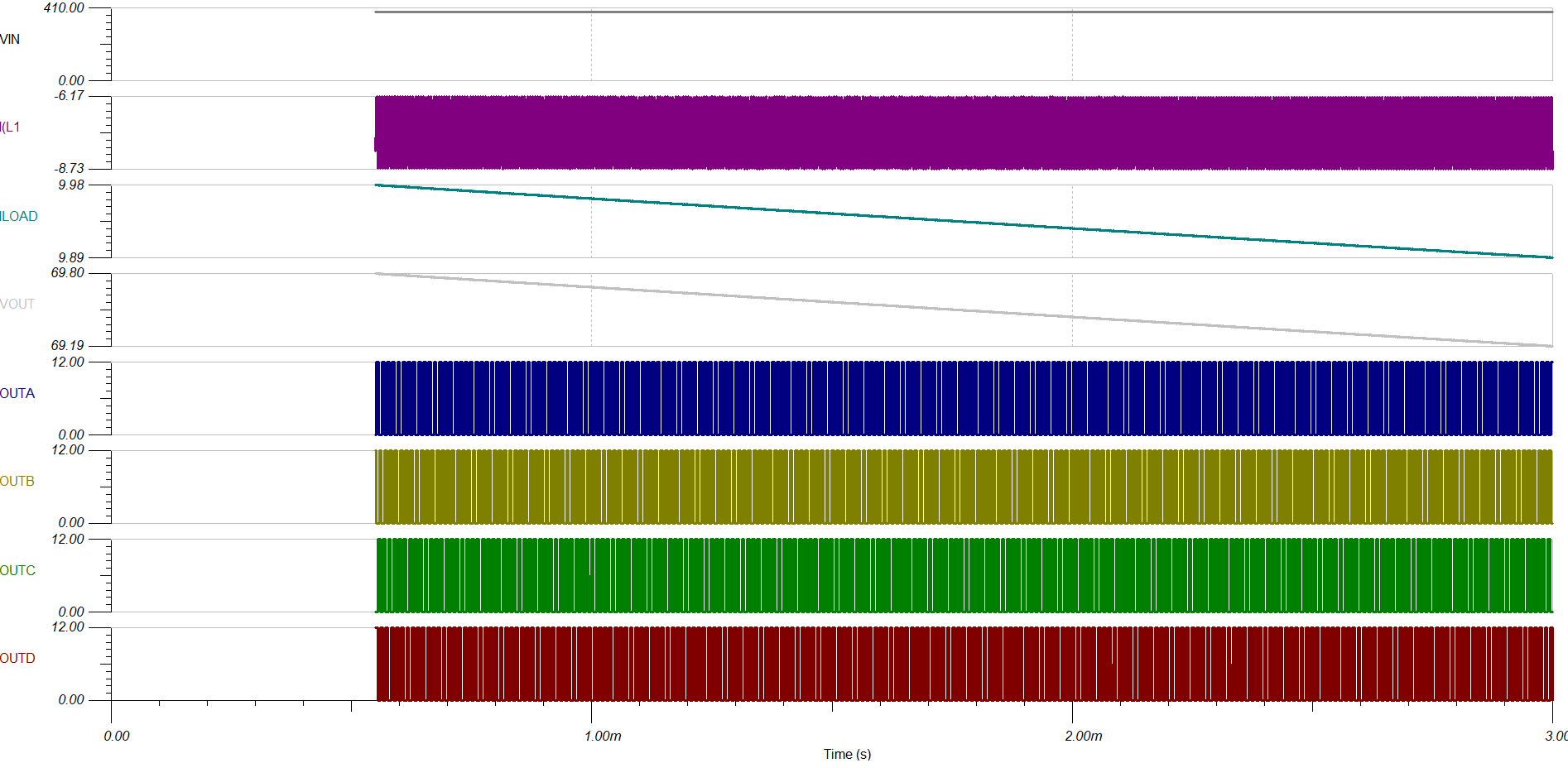

We are running out of the calculated budget to accommodate the input capacitor losses and the the mosfet power losses at the secondary side. Please find the attached excel sheet SLUC222D (version 1).xls

We are using the following parts

Qa,Qb, Qc, Qd mosfets: IPA60R145CFD7XKSA1 (part number)

Ls(shrimp inductor) : B82477P4392M

Cout : LKMD1151K820MF

What is the purpose of having 2 mosfets at the secondary side instead of diodes?

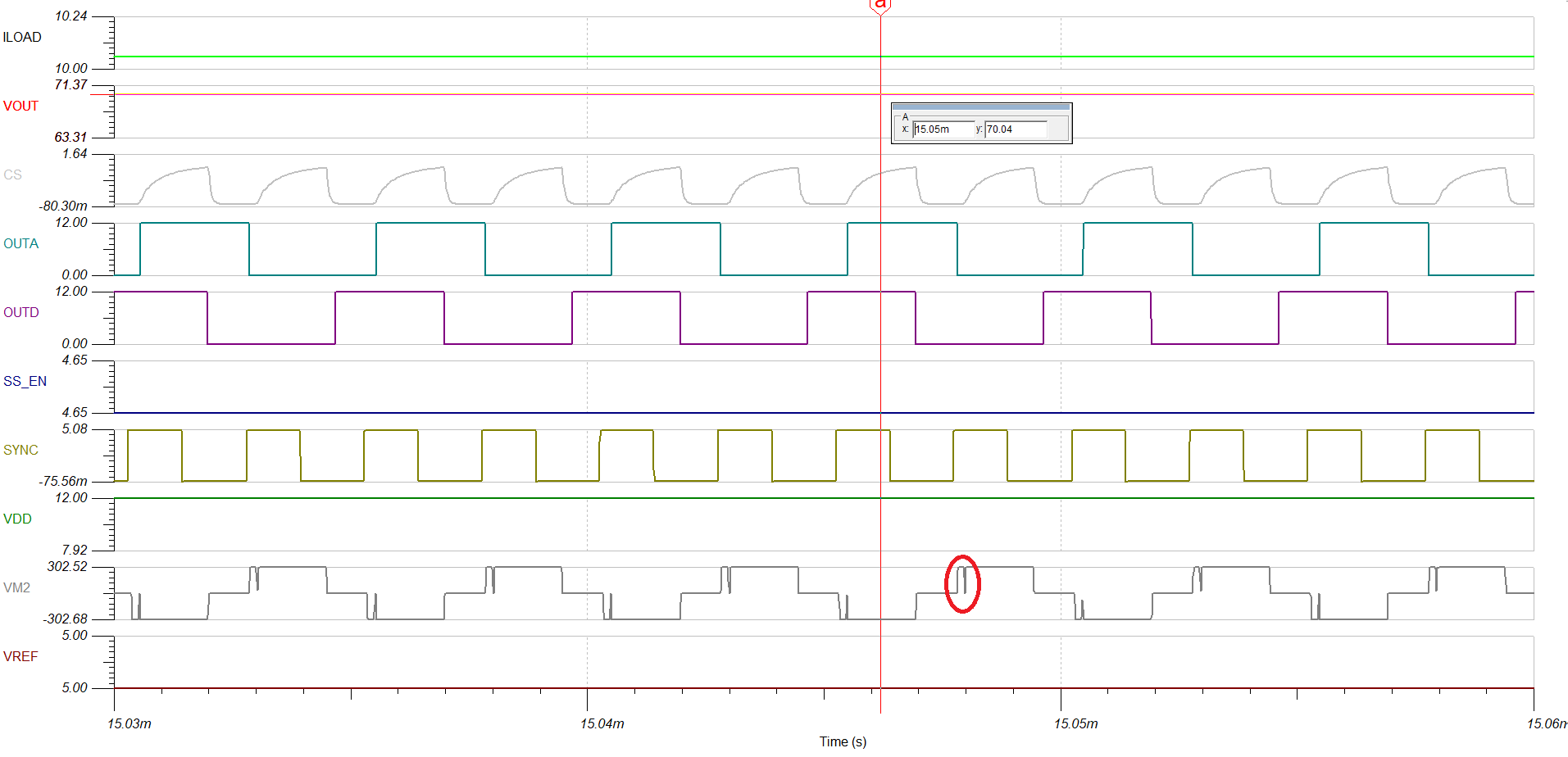

on page 11 of UCC28950 600-W, Phase-Shifted, Full-Bridge Application Report, the calculated voltage across secondary fets are Vin(max)/a, we have 388 Vin max and the turns ratio is 2. the voltage across fets on secondary should be 194V. but on the calculation tool, it reads 388V. for the selection of mosfet at secondary, which value should we go with? could you please suggest on this?

could you suggest parts for 70V DC, 10A, 700 W design so that twe can have efficiency of 94 % or above?

Thank-you

Warm Regards

Harini Krishna